## **Readout ASIC of Pair-monitor for ILC**

H.Ikeda <sup>A</sup>, K.Ito <sup>B</sup>, A.Miyamoto <sup>C</sup>, T.Nagamine <sup>B</sup>, R.Sasaki <sup>B</sup>, Y.Sato <sup>B</sup>, Y.Takubo <sup>B</sup>, T.Tauchi <sup>C</sup>, H.Yamamoto <sup>B</sup> A : JAXA, B: Tohoku University, C : KEK

> Presented by Yutaro Sato Tohoku university 14<sup>th</sup> Mar. 2009

### Outline

1

#### 1. Introduction

ilr

116

- International Linear Collider

- Pair-monitor

#### 2. Development of the readout ASIC

- Design and layout

- Operation test

- 3. Pair-monitor with SOI technology

- 4. Summary

## **1. Introduction**

*ifc* International Linear Collider

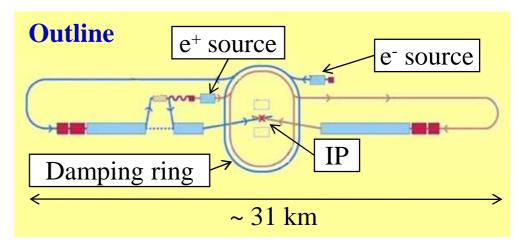

#### ILC (International Linear Collider)

Next generation of the high-energy  $e^+e^-$  collider

- Purpose

- Study Higgs, new physics ...

#### • Parameters

- CM energy : 500 GeV ( upgrade to 1 TeV)

- Integrated luminosity :  $2 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$

- $\rightarrow$  Beam profile monitor is necessary to keep the high luminosity.

### **Pair-monitor**

#### **Requirement to the beam profile monitor**

• Measurement accuracy of the beam size :  $< \sim 10 \%$

- Beam size : ( $\sigma_x, \sigma_y, \sigma_z$ ) = (639nm, 5.7nm, 300 $\mu$ m)

- Quick feed-back of measurement result

- No disturbance of other particle detectors

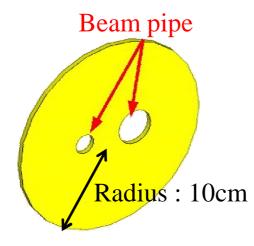

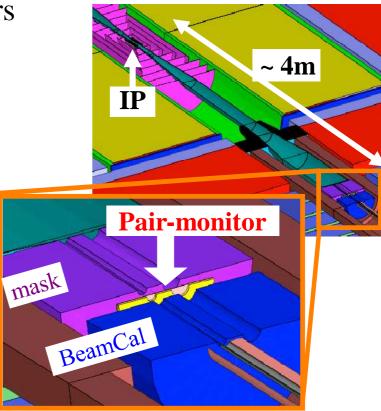

#### → Candidate : Pair-monitor

- Silicon pixel sensor

- Location : ~4m from IP

- Radius : 10cm

ilr

İİL

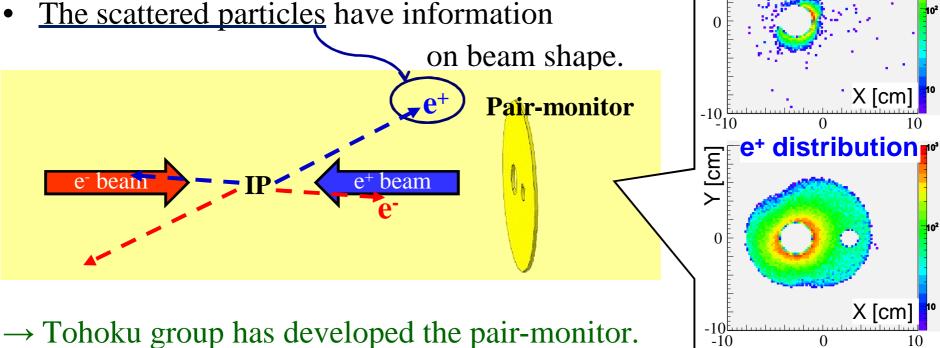

#### ilc **Beam profile measurement**

#### **Idea of the beam profile measurement** Pair-monitor measures $\sigma_x$ and $\sigma_y$ of the beam at IP, using the hit distribution of the pair B.G.

- A lot of the pair B.G are created during beam crossing.

- The same charges with respect to the oncoming beam are scattered with large angle.

- The scattered particles have information

e<sup>-</sup> distribution

۲ [cm]

## **2. Development of readout ASIC**

# **Development of the readout ASIC**

As the first step, readout ASIC was developed.

#### **Design concept of readout ASIC**

- Pair-monitor measures the hit distribution of the pair B.G.

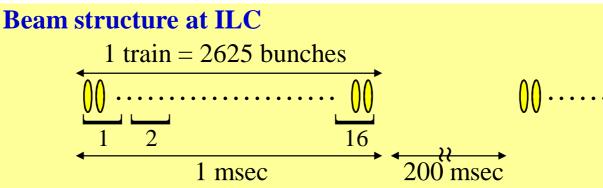

- Measurement is done for 16 parts in one train

for the time-dependent measurement.

- 16 Hit counts are stored at each part.

- Count rate : < 2.5 MHz / (400 $\mu$ m x 400 $\mu$ m)

- Information of the energy deposit is not necessary.

- Data is read out during inter-train gaps. ( ~ 200 msec )

$\rightarrow$  The prototype readout ASIC was designed to satisfy these concepts.

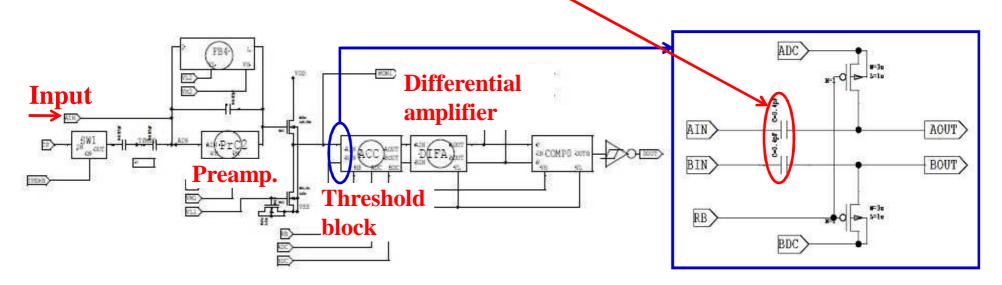

## **Design of readout ASIC**

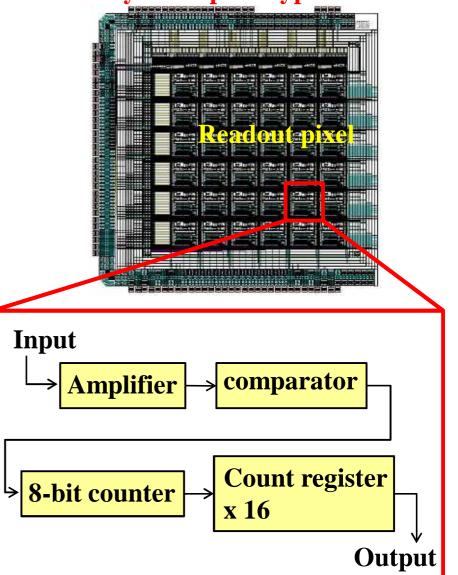

#### **Design of readout ASIC**

- 36 (6 x 6) readout pixels

- Amplifier

ilr

116

- comparator

- 8-bit counter

- $\succ$  to hit a number of hits

- 16 count-registers

- $\succ$  to store hit counts

- Shift register

- $\succ$  to select a pixel from 36 pixels

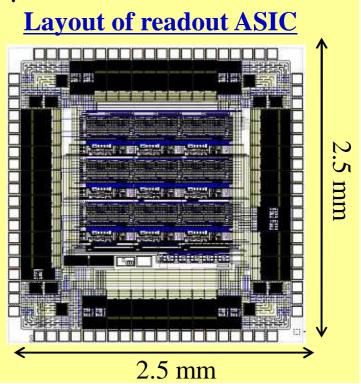

#### Layout of prototype ASIC

## **Prototype of Readout ASIC**

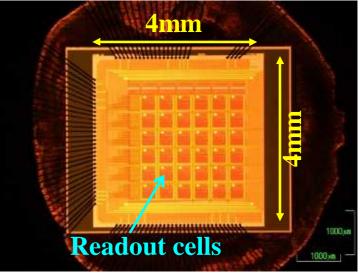

The prototype of the readout ASIC was developed.

#### **Prototype ASIC**

ilr

116

- Production process : 0.25 µm TSMC

- Chip size: 4 x 4mm<sup>2</sup>

- # of pixel : 36 ( = 6x6 )

- Pixel size :  $400 \times 400 \ \mu m^2$

- Sensor will be bump-bonded to the ASIC.

- The chip was packaged in a PGA144.

$\rightarrow$  The 3<sup>rd</sup> production of the readout ASIC was done in Oct. 2008.

$\rightarrow$  The trouble was found in the 1<sup>st</sup> and 2<sup>nd</sup> production.

### **Test system**

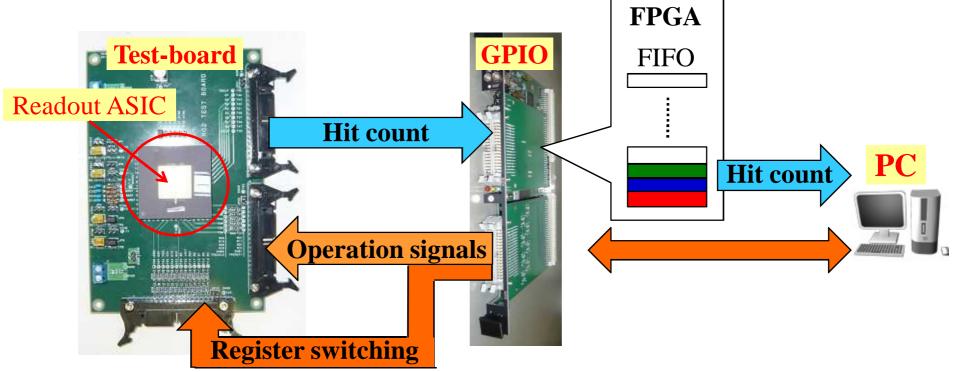

The operation test was performed.

#### Test system

- GNV-250 module was used for the operation and readout .

- KEK-VME 6U module

- The test-sequence by GPIO is controlled by <u>a PC.</u>

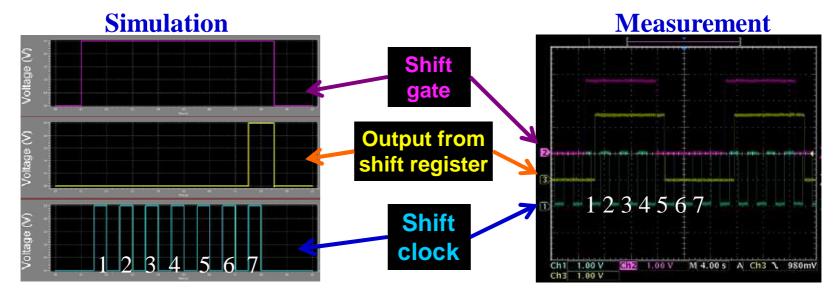

## **if** Problem in the 1<sup>st</sup> production (1)

The 1<sup>st</sup> production of the readout ASIC was done in 2006. **Problem**

- The shift register to select a readout pixel did not work correctly.

- The readout pixel is selected by the number of the shift clock.

Shift clock  $\rightarrow x_1 \rightarrow x_2 \rightarrow x_3 \rightarrow x_4 \rightarrow x_5 \rightarrow x_6 \rightarrow Output$

– Output should rise at 7<sup>th</sup> clock, and fall when the shift gate falls.

$\rightarrow$  The reason of the problem was investigated.

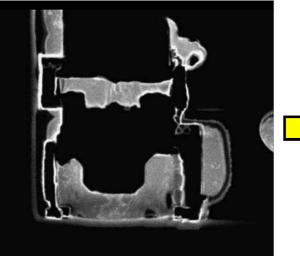

# **Problem in the 1<sup>st</sup> production (2)**

#### Reason

- The input register had disconnection.

- The layout information is not defined in the process library.

The disconnected input line was connected

with FIB (Focused Ion Beam) processing . (  $@VDEC \ sub-center \ of \ Osaka \ Univ. )$

**Exposed location of problem**

- After FIB processing, the shift register worked correctly.

- $\rightarrow$  The 2<sup>nd</sup> production was done with the input registers removed.

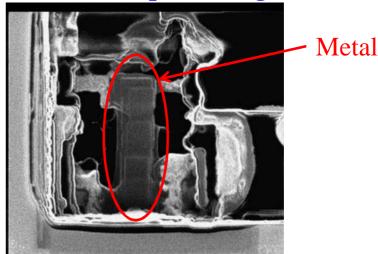

# *IC* Problem in the 2<sup>nd</sup> production

The 2<sup>nd</sup> production of the readout ASIC was done in 2007.

#### **Problem**

• The signal did not pass between pre-amplifier and threshold block.

#### Reason

• The layout mask for the MIM capacitor was missing due to a mistake.

$\rightarrow$  The 3<sup>rd</sup> production of the modified readout ASIC was done.

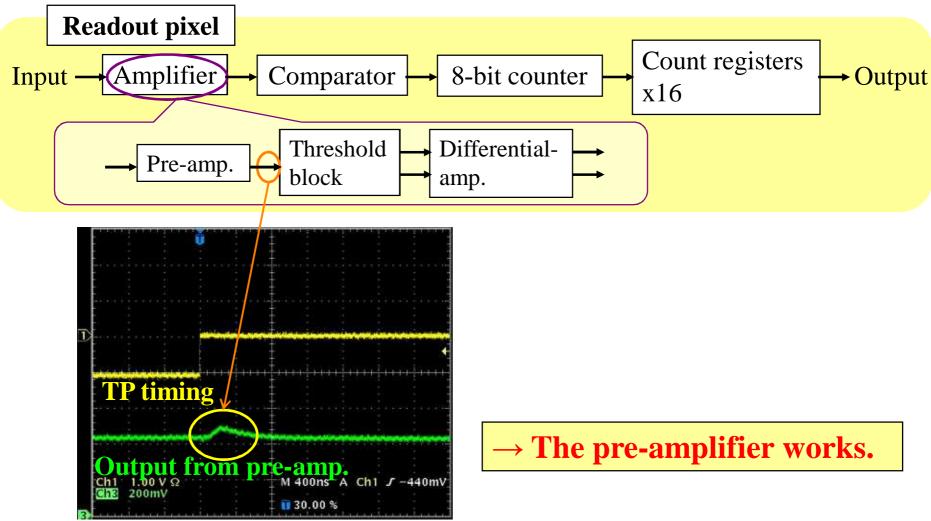

# **Response of pre-amplifier**

#### **Operation test of the 3<sup>rd</sup> production**

The response of the pre-amplifier was checked.

# **Response of differential-amplifier**

#### **Operation test of the 3<sup>rd</sup> production**

The response of the differential-amplifier was checked.

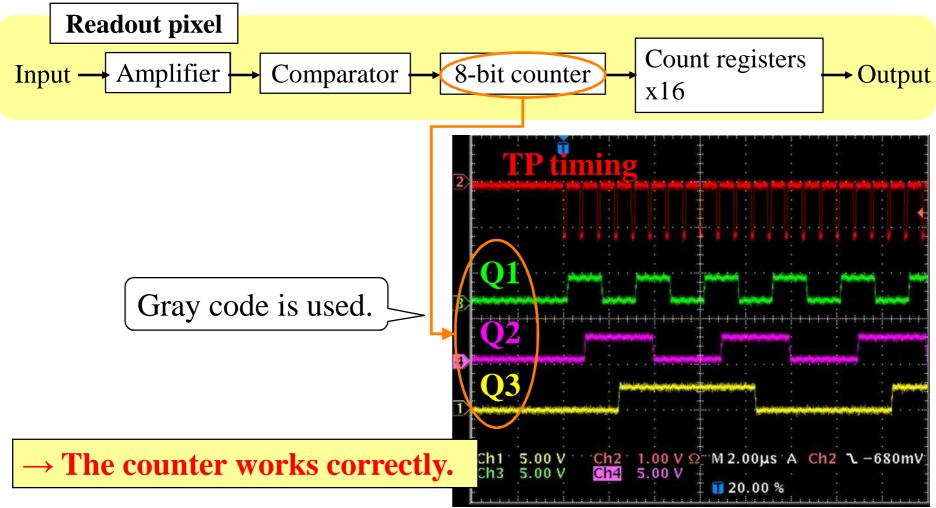

# **Response of counter block**

#### **Operation test of the 3<sup>rd</sup> production**

The response of the counter was checked.

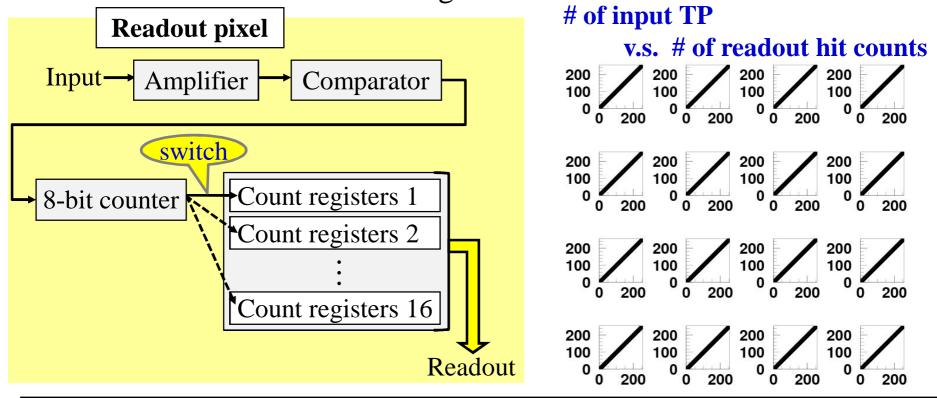

### **Readout of hit counts**

#### **Operation test of the 3<sup>rd</sup> production**

Readout of hit counts was checked.

ilr

IIL

• The hit count was stored at 2.5MHz hit rate/ (400µm x 400µm) and read out from the count registers.

The readout ASIC was confirmed to work correctly as designed.

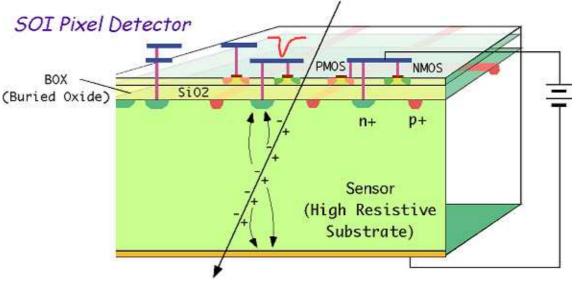

## **3.** Pair-monitor with SOI technology

# *IC* Pair-monitor with SOI technology

SOI (Silicon On Insulator) technology will be used for the development of the pair-monitor.

#### **SOI pixel detector**

- The sensor and readout electronics are integrated in the SOI substrate. (monolithic)

- High speed

- Lower power

- Thin device

- Low material

The development of the Pair-monitor with SOI technology was started, participating in MPW (Multi Project Wafer) Run at KEK.

### **Prototype of SOI chip**

For the next prototype, only the readout ASCI will be developed. The layout of the readout ASIC was finalized.

#### **Design of readout ASIC**

- Production process : FD SOI CMOS 0.2 μm

- Chip size : 2.5 x 2.5 mm<sup>2</sup>

- # of pixel : 9 ( = 3 x 3 )

The chip will be delivered in Apr., 2009.

# ilc

### Summary

- Beam profile monitor is necessary for high luminosity.

→ Pair-monitor

- The prototype of the readout ASIC was developed.

- The chip works correctly as designed.

- The chip will be connected with the PIN diode.

- The next readout ASIC will be developed

with **SOI** technology.

- The layout was finalized.

- The prototype will be delivered in Apr., 2009.

## Thank you for listening!