# PIXOR2 Double SOIのアナログ回路の性能評価

東北大学 素粒子実験研究室 学部4年 牛木至

# 目次

- ✓ SuperKEKB と Belle II

- ✓ SOI ∠PIXOR

- ✓ 評価試験

- ✓ 今後

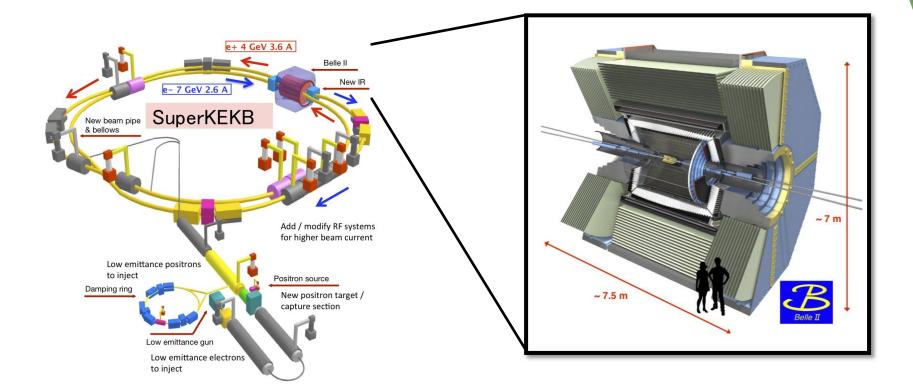

# SuperKEKB & Belle II

# SuperKEKB & Belle II

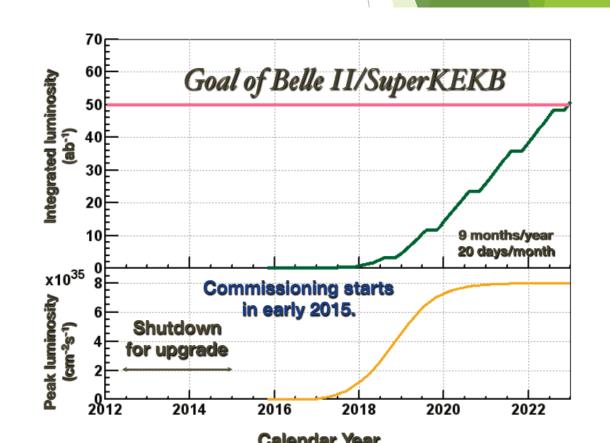

2016年に稼働予定

5年かけてピークルミノシティ8× $10^{35}$ cm<sup>-2</sup>s<sup>-1</sup> (Belle の40倍)

最終積分ルミノシティ50ab<sup>-1</sup> (Belleの50倍)

$e^-$ を7GeV、 $e^+$ を4GeVに加速して衝突させ、10.58GeVの共鳴状態Y(4S)を作り、

その崩壊先としてB中間子を大量に得る。

#### Belle IIで期待される物理

- 1.B中間子崩壊の精密測定

- 2. 右巻き相互作用の探索

- 3.荷電ヒッグスの探索

- 4.τのLFV探索

- 5.ハドロン物理

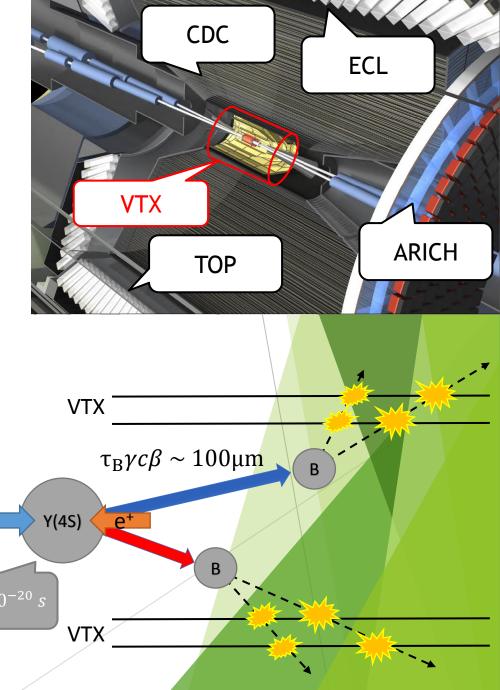

### 崩壞点検出器 VTX

VTX = PiXel Detector (PXD)+ Silicon Vertex Detector (SVD) 荷電粒子の軌跡を再構成(トラックを引く)

➡ B中間子の崩壊点(vertex)

$\frac{m_{\Upsilon(4S)}}{2}$ ~5.29GeVと $m_B$ ~5.28GeVがほぼ同じ

$\Upsilon(4S)$ の静止系では、 $B\bar{B}$  への崩壊では、  $\tau_B \sim 1.5 ps$  ほどの  $B\bar{B}$  は  $\beta\gamma \sim 0.06$ で  $\tau_B\gamma c\beta \sim 30 \mu m$ しか飛ばない。

非対称エネルギー7GeVと4GeVを用いることで、  $\beta\gamma\sim0.28$  を持ち、 $\tau_{\rm B}\gamma c\beta\sim100\mu{\rm m}$  飛ぶ。

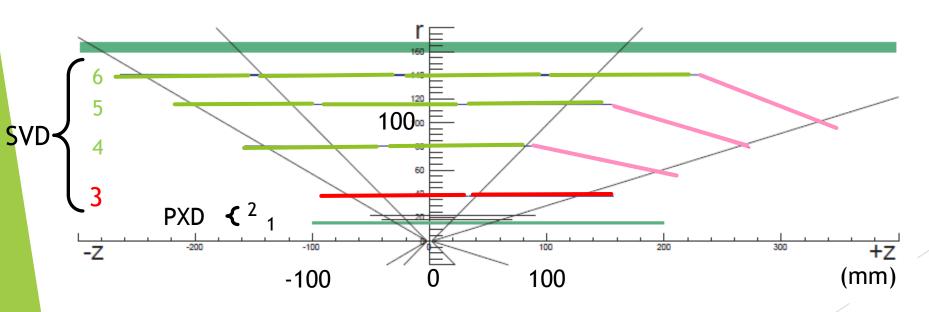

# 崩壊点検出器(VTX)

#### 要求

- ▶ 低物質量:外側の検出器で得たい情報を崩さない

- ▶ 低い占有率と細かな位置分解能:トラッキングの精度向上

VTXの典型的な占有率は1~3%

L3のSVDの占有率6.7%は高い

この層にPIXORを導入したい

| Layer | Radius<br>(mm) | Occupancy |

|-------|----------------|-----------|

| L6    | 140            | 0.9%      |

| L5    | 115            | 1.3%      |

| L4    | 80             | 2.7%      |

| L3    | 38             | 6.7%      |

| L2    | 22             | ~1%       |

| L1    | 13             | ~1%       |

SOI

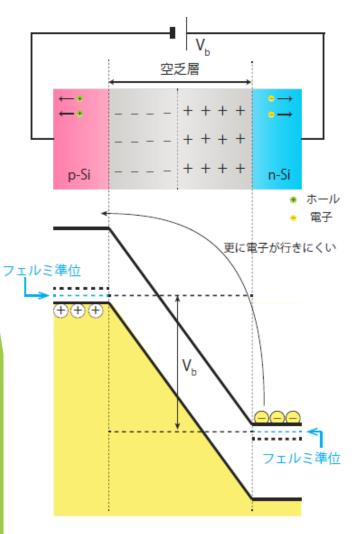

### 半導体素子

P型半導体とN型半導体を接合

- → ホールと電子が結合、キャリアなし(空乏層)

- → P型でホールの減少、N型で電子の減少

- →電位勾配の発生

スイッチとしての半導体素子

OFF: 勾配によってソースとドレイン間電流

は 流れない

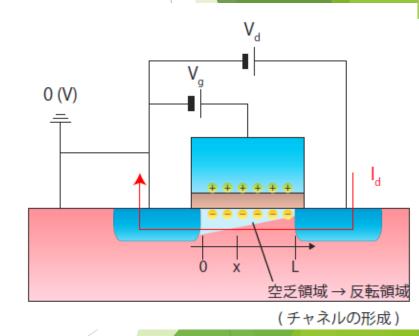

ON:ゲートに電圧を印加

- → ゲート下のホールが移動

- → N型に反転し電流が流れる

<u>チャンネルの形成</u>

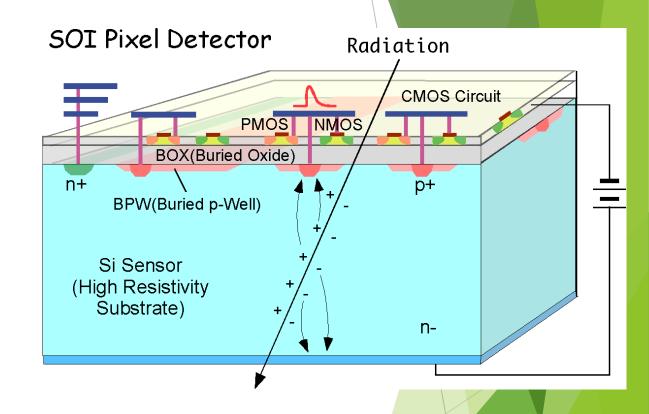

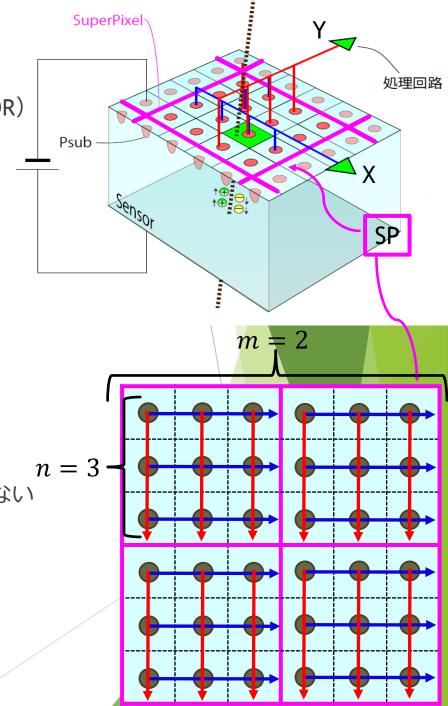

### SOI 検出器の紹介

SOI(Sillicon On Insulator): 半導体検出器

<u>ピクセル型</u>かつ、センサー層の上に処理回路のある<u>オンセンサー型</u>

処理回路とセンサー層が一体の半導体として作られている<u>モノリシック型</u>

物質量とコストの低下

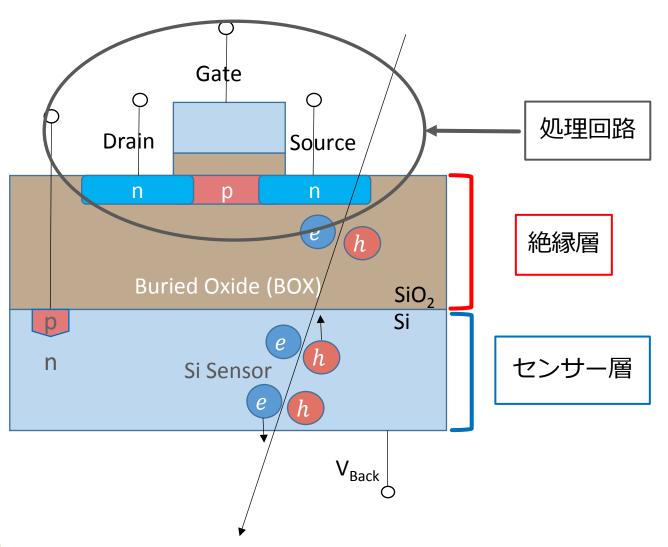

### SOI 検出器の紹介

処理回路とセンサー層が 絶縁層によって分離

#### メリット©

- 低消費電力、高速動作

- 広い動作温度

- 放射線耐性

#### デメリット🕾

バックチャンネルの形成……

#### 寄生容量:

設計者の意図しない容量成分 回路の特性変化につながる

B2JS 2014 March 1st

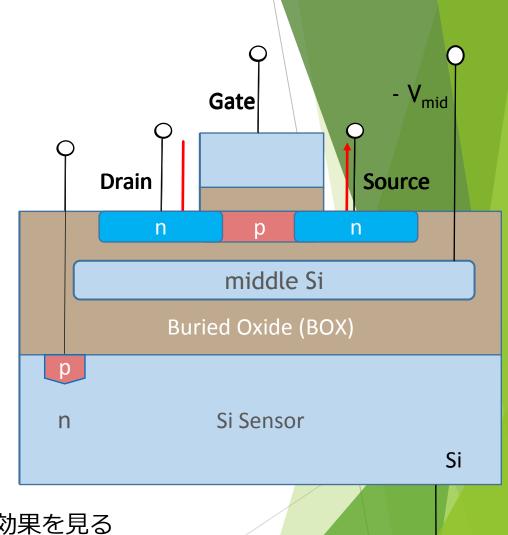

### Double SOI

絶縁層のデメリット窓

絶縁層にトラップされたホールが<u>バックチャンネル</u>を形成

→ ドレインとソースが導通

V<sub>BACK</sub>の影響で似た効果も発生

対策: Double SOI

絶縁層にシリコン層を入れて、電位を-V<sub>mid</sub>に固定

ホールによる電位を打ち消す♡

今回の試験では、Double SOIによるバックチャンネルの抑制の効果を見る

# **PIXOR**

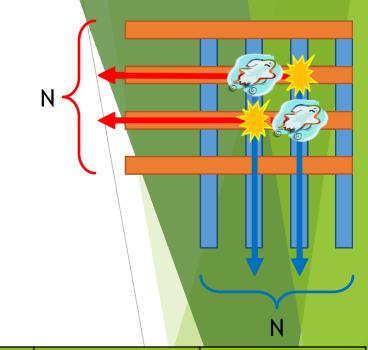

# ピクセル型とストリップ型の比較

#### ピクセル型のメリット、デメリット

#### ◎占有率

1 ヒットに対して占有率は、 $N \times N$  のピクセル型では $\propto 1/N^2$ 、

N + N のストリップ型では ∝ 2/2N = 1/N

#### ☺S/N比、物質量

センサー端子の面積が小さいため、寄生容量が小さくてノイズが小さい。その分シグナルも小さくてよいので、センサー層を薄くできる。

#### ◎ゴーストヒット

ピクセル型では発生しないが、ストリップ型では2つの同時ヒットがあると4つのヒット点が考えられる。

#### ※不感時間、位置分解能

オフセンサーでは、複数のピクセルを1つのチャンネルで読むため、不 感時間が大きい。オンセンサーでは、1ピクセルに1つの処理回路がある ため、処理回路の面積によってピクセルサイズに制限がかかる。

| 項目    | ピクセル    | ストリップ         |

|-------|---------|---------------|

| 占有率   | ○ (低い)  | <b>X</b> (高い) |

| S/N比  | ○ (高い)  | <b>X</b> (低い) |

| 物質量   | ○ (低い)  | <b>X</b> (高い) |

| ゴースト  | ○ (なし)  | 🗶 (あり)        |

| 不感時間  | × (長い)  | ◯ (短い)        |

| 位置分解能 | 🗶 (大きい) | ○ (小さい)       |

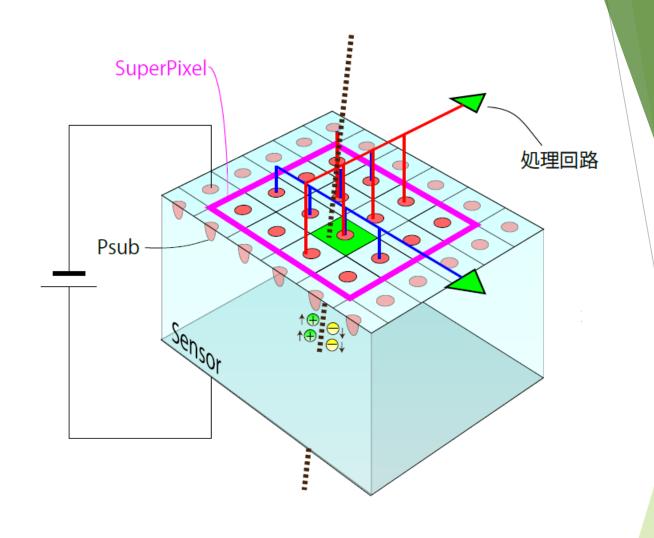

### PIXOR構造

SOI技術を使いピクセル、ストリップ型を組み合わせた構造: PIXOR (PIXel OR)

- N × N ピクセルを $n \times n$ ピクセルに区切る  $\rightarrow m \times m$  Super Pixel (SP) ( $N = n \times m$ )

- ▶ 1 SP 内で、XY方向に<u>ピクセルのORを取る</u>ことで、 SPがストリップ型のようになっている

n+nチャンネルのストリップ型(SP)が  $m \times m$ のピクセル型のように並んでるイメージ

- ◎ ストリップ型より占有率の低下

- ◎ ORの分ピクセル型より処理回路が少ない→ オンセンサーでも場所を取らない

- ◎違うSPでの同時ヒットではゴーストにはならない

# 試験

PIXOR2 アナログ回路評価

# PIXOR2 アナログ回路評価

高い電圧を $V_{BACK}$  に印加して空乏層を広げる  $V_{BACK}$  は状況によって変化させるかもしれない  $V_{BACK}$ による影響がないか調べたい

テストパルス $V_{\rm in}=200 [{\rm mV}]$ ,  $25 {\rm kHz}$ に対しての ${\rm Preamp}$ と ${\rm Shaper}$ の出力波形、それぞれのゲインの値を $V_{\rm BACK}=\{0,5,10,30,50,100\}$ [V]に変えて取得

$$GAIN = \frac{V_{out}}{Q_{in}} [\mu V/e]$$

*V*<sub>out</sub>[V]: 出力波形の振幅

$Q_{\rm in}$  [e] : テストパルスの振幅 $V_{\rm in}$ を

電子数に変換したもの (Q = CV)

$Q_{\rm in} \times 1.6 \times 10^{-19} [\rm C] = 4 [\rm fF] \times V_{\rm in} [\rm V]$

Sensor AIN Amp Out Amp Out Test Pulse DMOS ↔ コンデンサー厚50[µm]を通った) n p n

200[mV]は5000eに対応(MIPの作る100[e/ $\mu$ m]がセンサー厚50[ $\mu$ m]を通った)  $V_{\rm mid}=0.1V$ に固定して行った

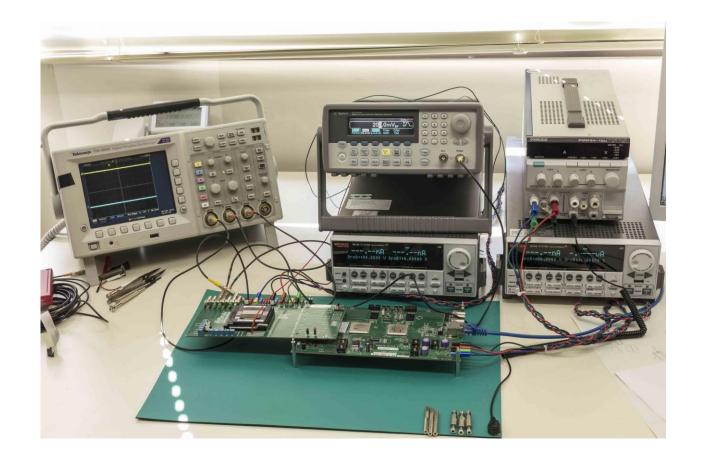

# 実験のセットアップ

オシロ、パルスジェネレータ、電源 **SEABAS** JOSA-TA-SAS **FPGA PIXOR** Sub Board

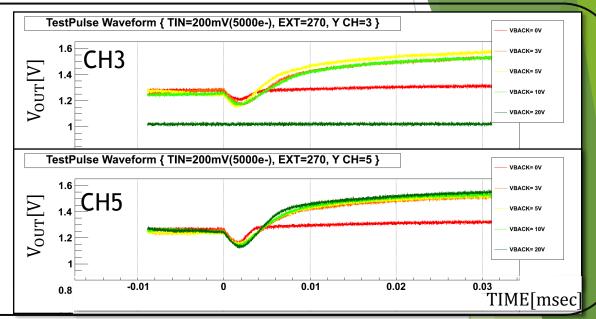

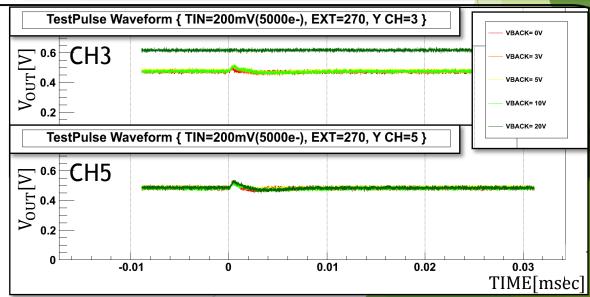

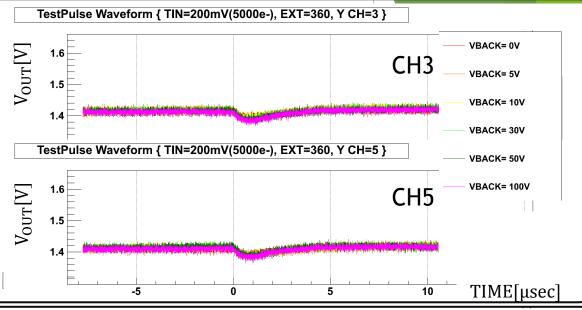

### PIXOR2 Single SOIの結果 V<sub>BACK</sub> = 0 ~ 20V, Y方向のCH3, 5のオシロの波形

#### Preampの出力

$V_{\text{BACK}}$ が20Vになると**CH**によって応答が違う 全く反応しないもの、ちゃんと増幅するもの

Shaperの出力 応答はとても小さい

# PIXOR2 Single SOIの結果

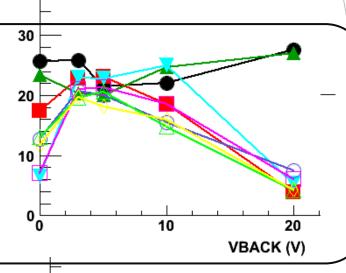

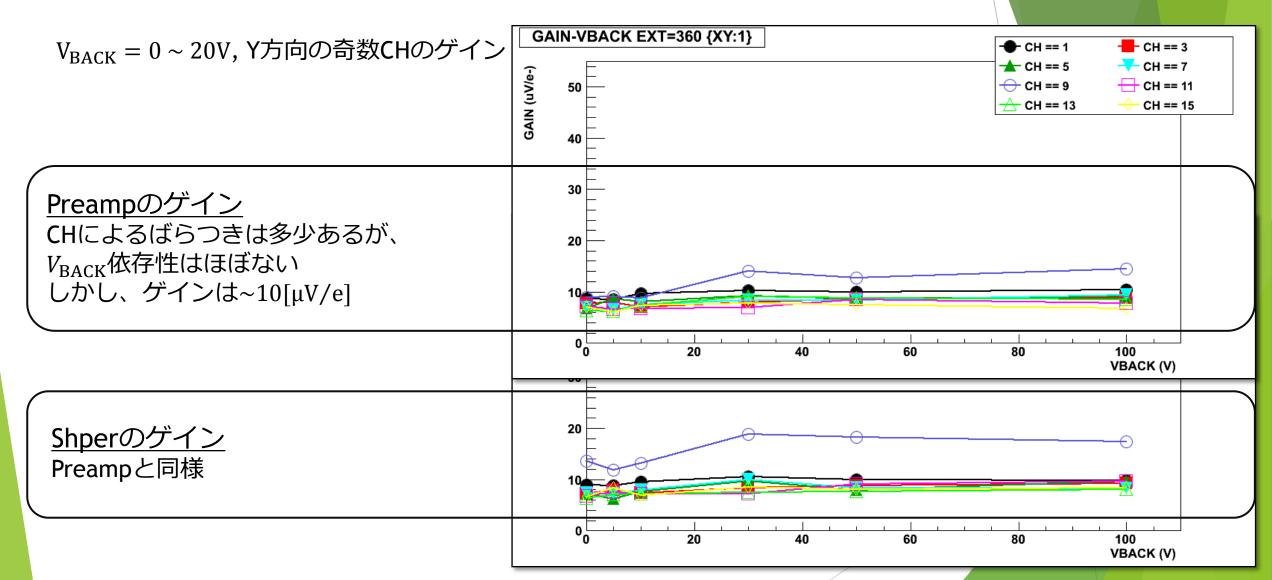

$V_{BACK} = 0 \sim 20V, Y方向の奇数CHのゲイン$

#### GAIN-VBACK EXT=270 {XY:1}

Preampのゲイン CHによるばらつきや $V_{BACK} = 20V$ でのゲインの減少が見られる

#### <u>Shperのゲイン</u>

Preampのゲインの形を引き継いでいる  $\sim 10 [\mu V/e]$  はとても小さな値

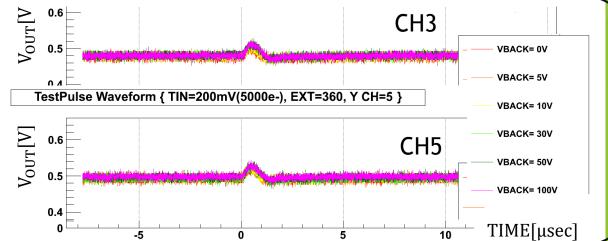

### PIXOR2 Double SOI の結果

$V_{BACK} = 0 \sim 100V$ , Y方向のCH3, 5のオシロの波形

#### Preampの出力

$V_{\rm BACK} = 100V$ まで一様に反応している CHやXY方向に対するばらつきもない

Shaperの出力 同様に依存性無く応答している

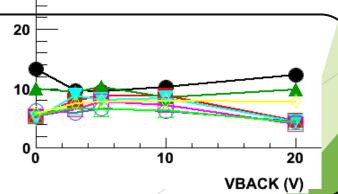

### PIXOR2 Double SOIの結果

# 考察

Double SOI構造を導入することで  $V_{\mathrm{BACK}}$ 依存性をなくすことができた

しかし、ゲインの値は小さいまま PIXOR1では $\sim 60[\mu V/e]$ ほどが得られていた PIXOR1と2の主な違いは,ピクセルサイズとOR数

| 変更点     | PIXOR1                                            | PIXOR2                                            |

|---------|---------------------------------------------------|---------------------------------------------------|

| ピクセルサイズ | $25[\mu\text{m}](\phi) \times 40[\mu\text{m}](z)$ | $35[\mu\text{m}](\phi) \times 70[\mu\text{m}](z)$ |

| OR数     | 4                                                 | 16                                                |

この違いにより寄生容量が増加し、ゲインが減少した

解決策:OR数を減らすか、回路のレイアウトを変更

# 今後

PIXOR3とPIXOR3 TEGがすでに製造されている

#### 変更点:

- センサー層N型→ P型、

- レイアウトの変更

- PIXOR3 TEGでの各回路要素の試験

- PIXOR3 (16×16のSPを4×7、総画素数2688) の全体動作試験

試験のためのPIXOR3専用の試験基盤の機能、レイアウトを考え、発注

→ 試験基盤ができたら試験

#### 東北大として

複数枚のPIXORを用いてビームテストを行い、トラックを引く Belle IIが稼働して5年後ルミノシティが最大値となるときの導入を目指す

# ありがとうございました