# Development of Readout ASIC for FPCCD Vertex Detector

01 October 2009

Kennosuke.Itagaki

Tohoku University

#### FPCCD Vertex Detector

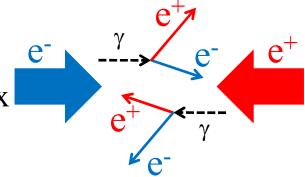

- Large amounts of e<sup>+</sup>•e<sup>-</sup> pair background is generated at beam collision.

- For low pixel occupancy, we develop Vertex Detector adopt fine pixel CCD sensor.

120mm

- FPCCD Vertex Detector

- Fine Pixel CCD

- $\triangleright$  Pixel size : 5 $\mu$ m  $\times$  5 $\mu$ m

- > Epitaxial layer thickness: 15μm

- $-20,000 \times 128 \text{ pix/ch}$

- # of channels  $\sim 6,000$ ch

- Double layers : CCDs are attached on two sides of the ladders.

- Readout ASIC for FPCCD is developed.

## Requirements to readout ASIC

- Power consumption < 6 mW/ch

- > Setting in a cryostat

- ➤ Total power consumption < 100W

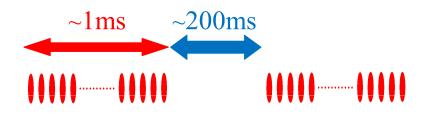

- Readout rate > 10 Mpix/sec

- > Read out in the inter-train time

- $\geq$  20,000 × 128 pix / 200 ms

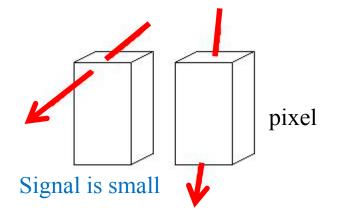

- Noise level < 30 electrons

- ➤ Signal becomes small for particles penetrating with large angle.

Readout ASIC was designed to satisfy these requirement.

## Solution of Requirements

- Power consumption < 6 mW/ch

- ➤ ADC is the main power consumption source.

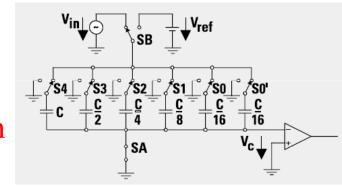

- For suppressing power consumption at ADC, charge sharing ADC is used.

- Signal is converted by comparing the reference voltage with a capacitor.

- $\Rightarrow$  Power consumption of ADC < 10μW/ch

- Readout rate > 10 Mpix/sec

- ➤ It is difficult to operate charge sharing ADC with high-speed

- Two 5MHzADC are used alternatively.

- → 10Mpix/sec

- Estimated noise level < 30e

## Test sample of readout ASIC

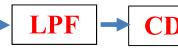

- Design of prototype ASIC

- Amplifier

- Low pass filter (LPF)

- Correlated double sampling (CDS)

- > sample backward and forward of pixel data

- > output voltage difference at sampling points

- Charge sharing ADC × 2

- Serial output

CCD output

CDS output

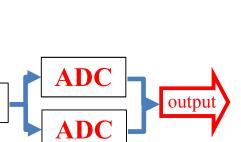

• Test sample

0.35μm TSMC process

Chip size :  $2.85 \text{ mm} \times 2.85 \text{ mm}$

# of channels: 8

Package: QFP-80 pin

sampling

The performance of a test sample was checked

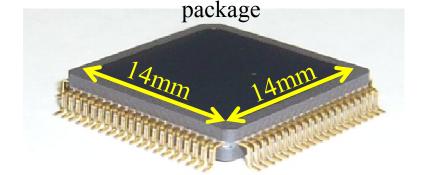

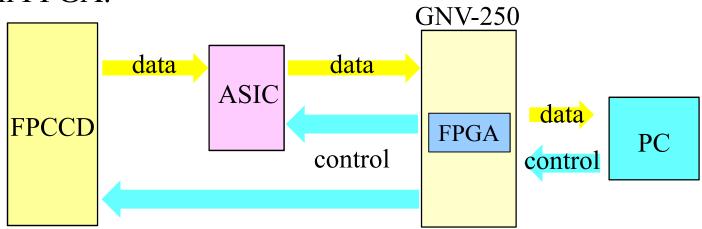

#### Test bench

- Data acquisition and circuit control are done by a VME module.

- GNV-250 module

- The control logic was implemented into FPGA.

- The test job and parameter setting are controlled by PC.

- ADC output is stored on FIFO embedded in FPGA, and sent to PC.

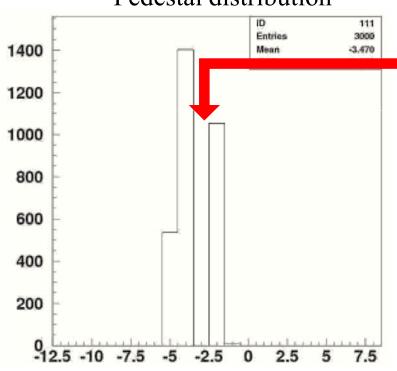

#### Pedestal distribution

- Pedestal distribution was checked

- − Conversion rate ~1.5 Mpix/sec

- Some ADC counts are not output.

- The reason was investigated.

- → Next slide

- Noise level

RMS = 1.1

Equivalent noise charge at sensor input

- $\Rightarrow$  ~45e (Requirement:30e)

- ADC count → Temperature dependency was checked.

- → After the next slide

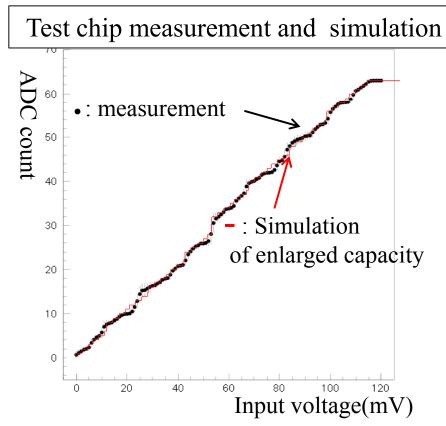

## Problem of ADC design

• ADC output was simulated by MATLAB.

• Simulation result of enlarged capacity of ADC capacitor is

consistent with measurement.

Charge sharing ADC

VTP

VQP

CTP

CSP

Capacitor array

VTN

VQN

VQN

- The floating capacitance at the switching circuit in the ADC unbalanced the ADC capacitor ratio.

- The switching circuit was designed again.

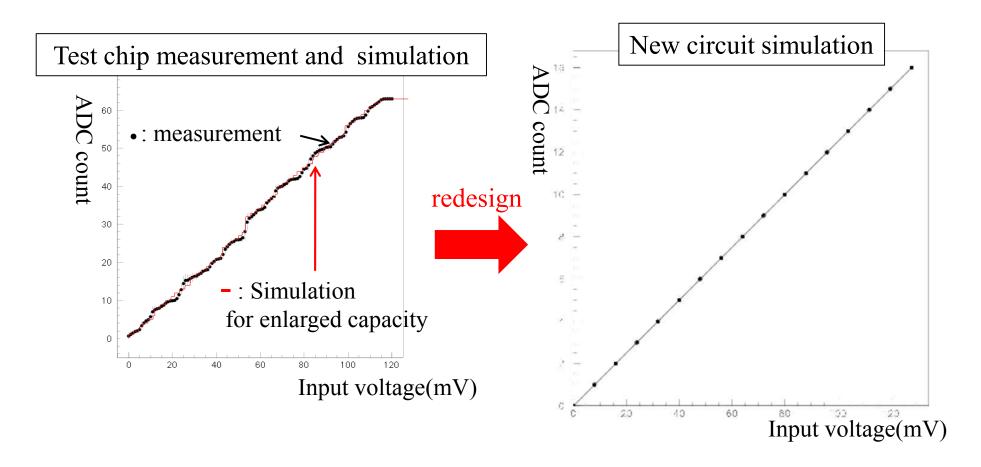

#### New circuit

• ADC output was checked by simulation with new switching circuit.

New circuit has no problem, and is adopted to the next sample.

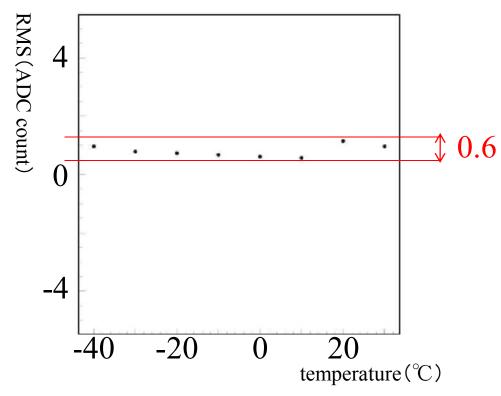

#### Temperature dependency of Pedestal

• The pedestal distribution was measured for various temperature.

- The main fluctuation of RMS comes from effect of the missing ADC counts.

- The temperature dependency is smaller than the RMS fluctuation.

- The temperature dependency will be studied with the next sample.

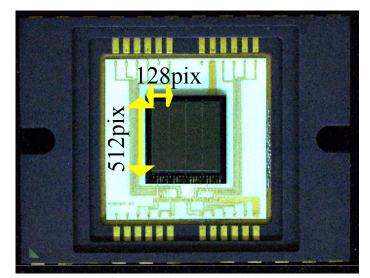

## Fine Pixel CCD sample

- Test sample to establish technology

- Pixel size:  $12\mu m \times 12\mu m$

- Epitaxial layer thickness: 15μm

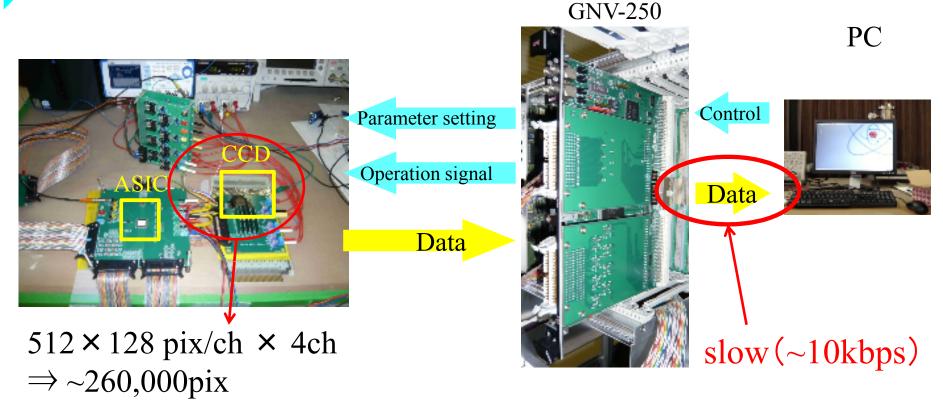

- # of readout channels: 4ch

- $\gt{5}12 \times 128 \text{ pix/ch}$

- FPCCD and readout ASIC were connected.

- The control logic for CCD was also implemented on FPGA.

#### FPCCD readout

- Speed transmission of VME module to PC is slow.

- ADC output is temporarily stored in FIFO.

- By limit of FPGA capacity, all the data cannot be stored.

- ADC data were converted to 1bit.

- Threshold: 30

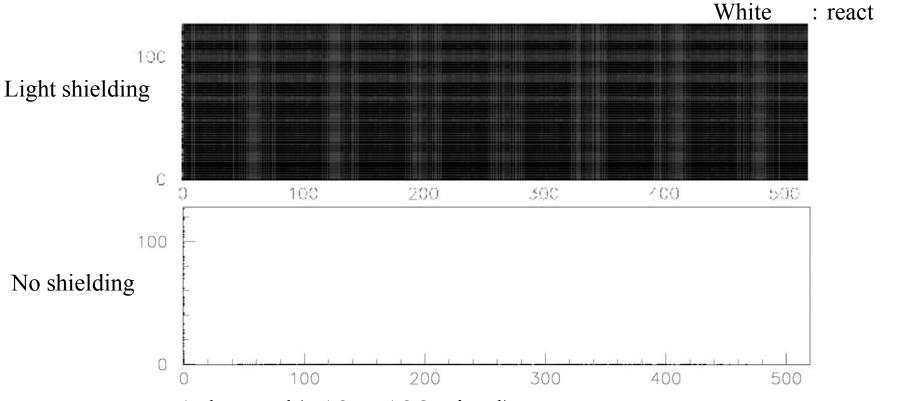

## FPCCD reaction for light

Black

: do not react

• Response of FPCCD to the light was checked.

- 1channel( $512 \times 128 \text{ pixel}$ )

- Response of FPCCD to the light emission can be observed.

- The image will be read as the next step.

### Summary

- We developed FPCCD vertex detector

- > Requirement for readout ASIC

- ◆ Power consumption < 6mW/ch</p>

- ◆ Readout rate > 10Mpix/sec

- ◆ Noise level < 30e

- Pedestal check for readout ASIC sample

- > Noise level ~ 45e

- > Some ADC count are not output.

- ⇒ switching circuit was designed again.

- > Temperature dependency of ASIC cannot be observed because of missing ADC.

- examined next sample

- FPCCD sample readout

- > By limit of FPGA capacity, all pixel cannot read out.

- ⇒ ADC data were converted 1bit.

- > Readout ASIC can read out FPCCD data

- → Next step is readout image

- > Readout board can read out all pixel is developed and tested.

## Buck up

## Power consumption of LVDS

- Differential voltage: 350mV

- Resistor :  $100\Omega$

- Power consumption :  $(350 \text{mV})^2 / 100\Omega = 1.2 \text{mW}$

- Below 6mV