#### ILCのためのFPCCD読み出し回路の開発

#### 9/14 東北大理 板垣憲之輔

東北大理、JAXA-ISASA、高工研<sup>B</sup> 齋藤智之、池田博一A、杉本康博<sup>B</sup>、田窪洋介、宮本彰也<sup>B</sup>、山本均

#### 内容

- 国際リニアコライダー (ILC)

- FPCCDバーテックス検出器

- FPCCD用読み出し回路

- 試験

- まとめ

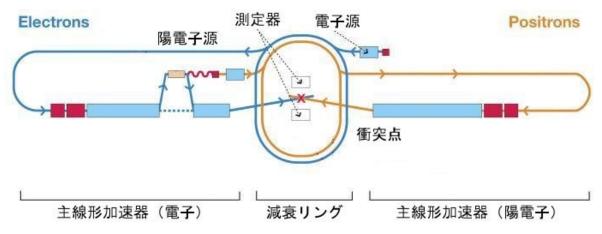

## 国際リニアコライダー(ILC)

- 電子•陽電子衝突型線形加速器

- 重心系エネルギー: 最大 500 GeV (アップグレード後: 最大1TeV)

- 積分ルミノシティ(四年間):500 fb-1

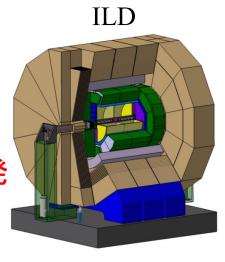

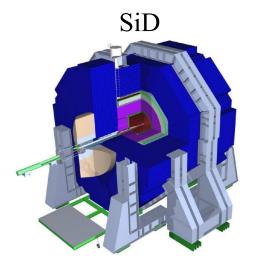

- ・ ILCの測定器

- ILD → アジア、ヨーロッパ

- SiD → 北米

- →ILDのバーテックス検出器を開発

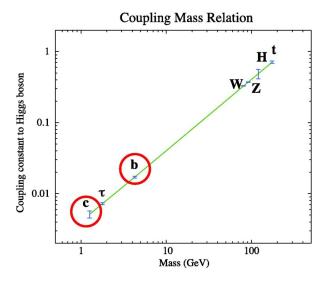

# FPCCDバーテックス検出器

- ・ バーテックス検出器への要求

- ヒッグス(H→bb,cc)の精密測定のための高い位置分解能

$$> \sigma = 5 \oplus \frac{10}{p\beta \sin^{3/2} \theta} (\mu m)$$

#### → FPCCDバーテックス検出器を開発

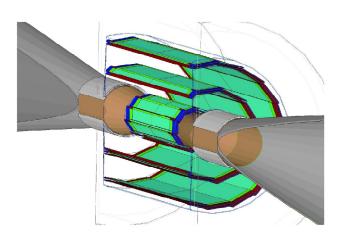

- FPCCDバーテックス検出器

- ピクセルサイズ: 5 μm × 5 μm

- 有感層の厚さ: 15 μm(全空乏)

- 総チャンネル数:6,080 チャンネル

- $20,000 \times 128 \text{ pix/ch}$

- 総ピクセル数:約10<sup>10</sup> ピクセル

# FPCCDバーテックス検出器

- 優れた点

- 空間分解能

- »高精細CCDによる

- 二粒子分解能

- » 全空乏化した有感層 → 信号電荷の熱拡散を抑制

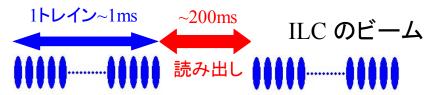

- ビーム由来の高周波ノイズから影響を受けない

- »トレイン間に読み出すことを前提に開発している

- バーテックス検出器実現のためには、読み出し技術の確立が必須

- センサーが高精細であるため、ピクセル数が膨大

- 200 ms に全ピクセルを読み出さなくてはならない

- → FPCCD用読み出し回路の開発

#### 4

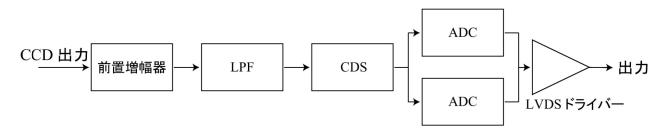

## 読み出し回路のデザイン

#### 読み出し回路への要求と対策

- □ 消費電力 < 6 mW/ch : クライオスタット内で冷却</p>

- ➤ 主な電力消費源: ADC, 信号の出力回路

- > 電荷再分配型ADCを使用:消費電力 ~ 10 μW/ch

- ➤ 出力信号 LVDS:消費電力~1.65 mW/ch

- □ 読み出し速度 > 10 Mpix/sec : 20,000 × 128 pix / 200 ms

- ▶ 5 Mpix/secの読み出し速度を持つADCを二つ用いる

- □ ノイズレベル < 30 電子:信号レベル ~ 500 電子

- ➤ LPF、相関二重サンプリング回路(CDS)を使用

→ 以上のデザインで読み出し回路を製作

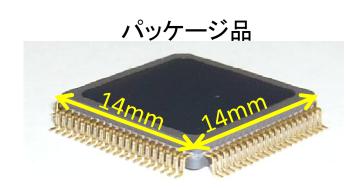

# 読み出し回路の試作

試作品

0.35μmTSMCプロセス

チップサイズ: 2.85 mm × 2.85 mm

チャンネル数:8

パッケージ: QFP-80ピン

#### • 試作品の単体性能

- 消費電力:~13 mW (全体) → O

- ノイズレベル:~28 電子 → ○

- 読み出し速度:~1.5 Mpix/sec → ×

- 一部のADCカウントが出力しない

⇒ 試作FPCCD の読み出し試験をおこなった

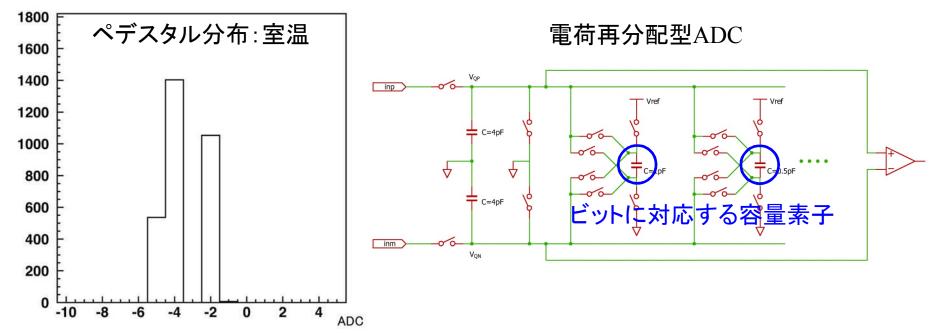

#### ペデスタル分布

#### 6

# 試作FPCCDの読み出し

- 試作FPCCD

- ピクセルサイズ: 12 × 12 μm<sup>2</sup> ← 実機: 5 × 5 μm<sup>2</sup>

- 有感層の厚さ:15 μm

- $-512 \times 128 \text{ pix/ch x 4 channel}$

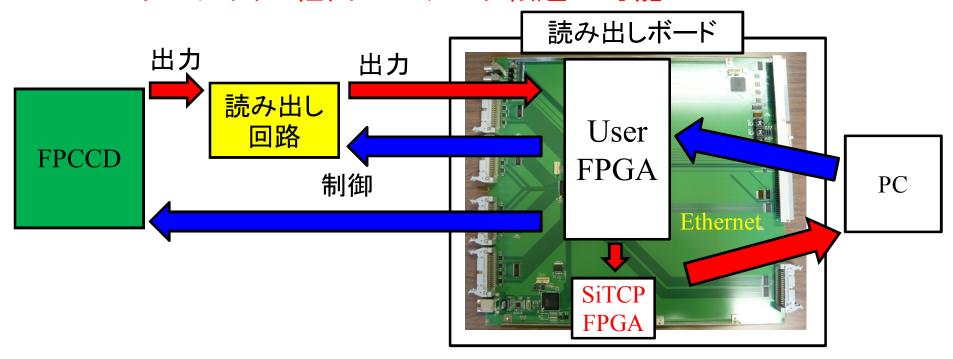

# FPCCD読み出しのセットアップ

- FPCCD読み出し用ボード

- User FPGA

- FPCCDと読み出し回路の制御ロジックを実装

- SiTCP FPGA

- イーサネット経由でのデータ転送が可能

→ 試作FPCCD を試作読み出し回路を用いて評価した

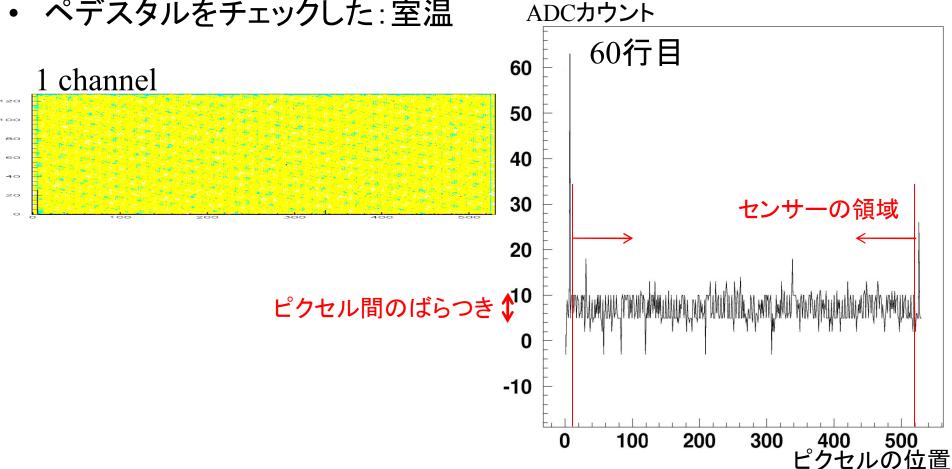

#### ペデスタル:室温

ペデスタルをチェックした:室温

- 両端のピークは最端のダミー部分 → センサーの領域外

- ノイズがのっている

- ⇒ 冷却して、ノイズの変化を確認した

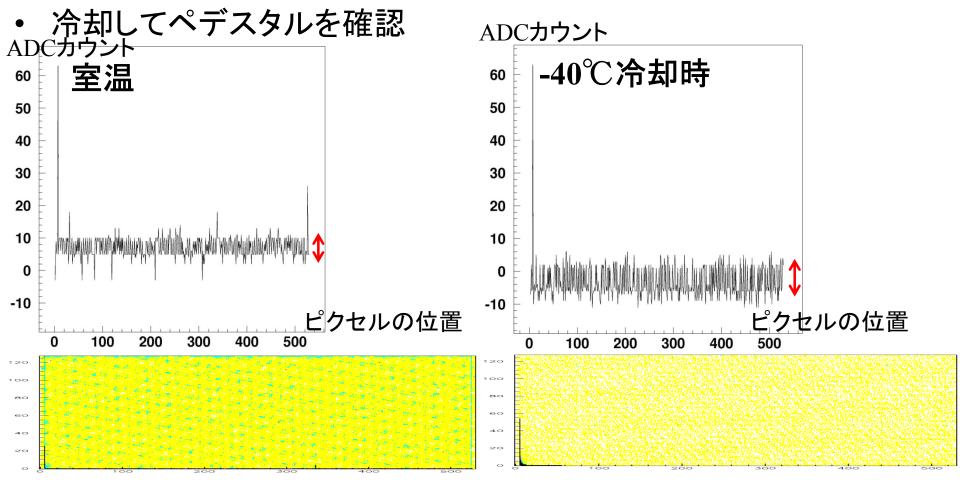

#### ペデスタル

- 冷却することでノイズは抑えられた

- ピクセルごとのばらつきは大きくなった

- → 1 pixel ごとのペデスタルを見た

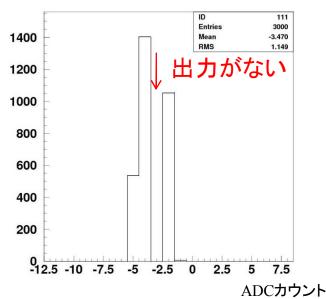

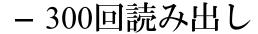

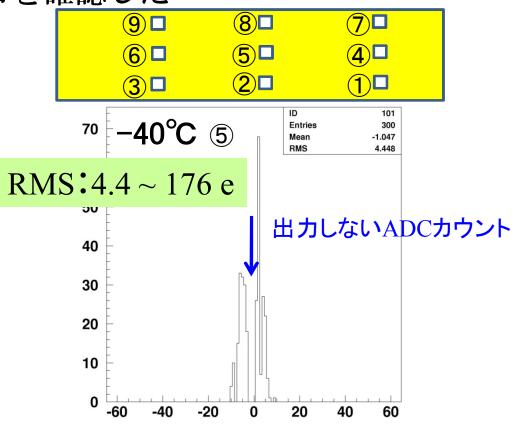

# ペデスタル:1pixel

CCD1pixelのペデスタル分布を確認した

- 9 pixelで確認

- 冷却すると広がる

- ピクセルごとのばらつきが大きくなる原因

- 出力しないADCカウントの影響

- ・ 読み出し回路の問題 → 次回試作で改善

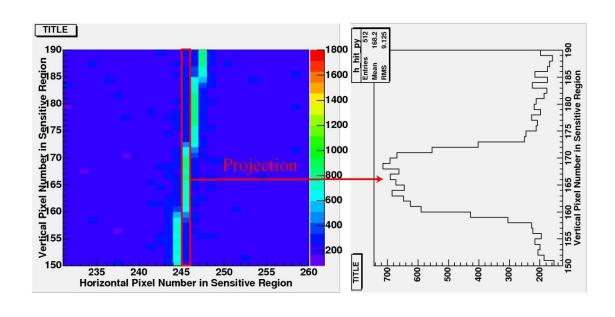

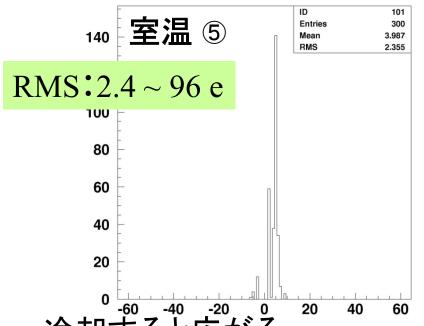

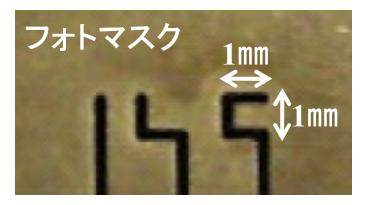

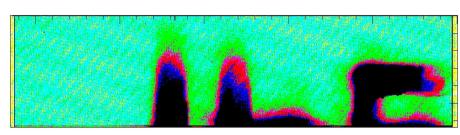

### 画像取得

- フォトマスクを被せ、二次元の画像を取得した

- 光源:LED (0.2 s)

- フォトマスク:ILC

- 文字サイズ:1 mm角

- ピッチ: 0.2 mm

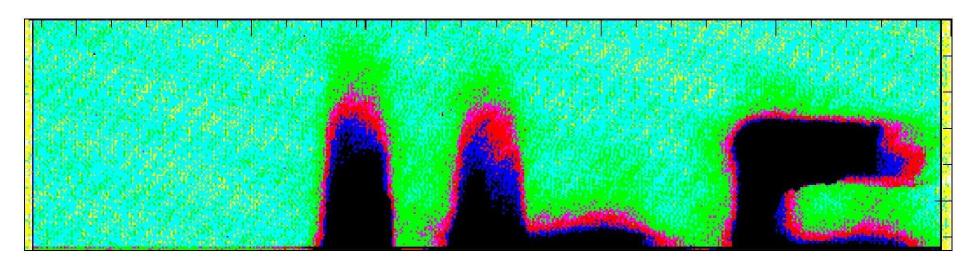

読みだした画像

→ ILC を読み出せた

### まとめ

- FPCCDバーテックス検出器を開発している

- 試作読み出し回路

- 消費電力 < 6 mW/ch → O

- ノイズレベル < 30 電子 → ○</p>

- 読み出し速度 > 10 Mpix/sec → ~1.5 Mpix/sec

- 一部のADCカウントが出力しない

- → 読み出し回路の再設計・製作が進んでいる

- 試作FPCCDの性能を試作読み出し回路で評価

- 冷却するとペデスタルの中心に出力しないADCカウントが位置 する

- → ペデスタルが広がる

- 画像を取得

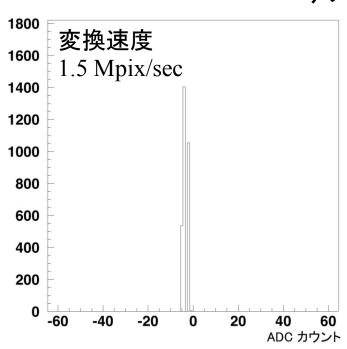

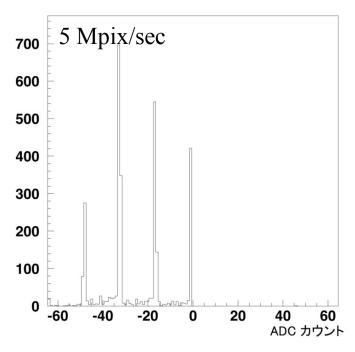

## 試作読み出し回路の性能

- 読み出し速度 ~1.5 Mpix/sec

- ➤ 1.5 Mpix/sec以上の変換速度でADC分布が広がる

#### ペデスタル分布

- ▶ 原因:コンパレータに流入する電流が不足

- → 次回試作で電源を強化

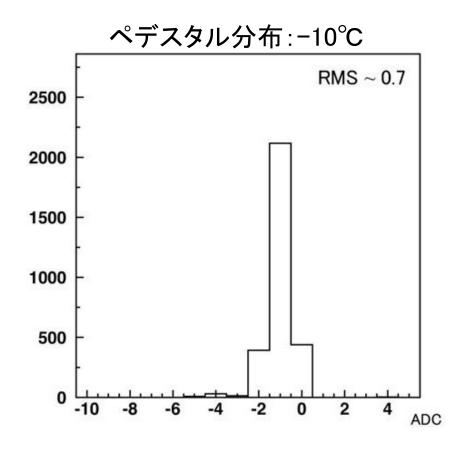

# ノイズレベルの測定

- ペデスタル分布

- 読み出し速度 ~1.5 Mpix/sec

- ノイズの見積り

- $-RMS = 0.7 \sim 28e$  (要求:30e)

- → ノイズの要求を満たせている

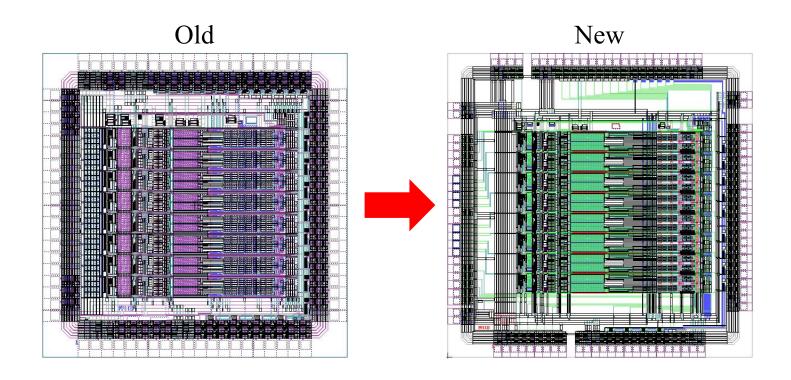

#### ADCの改良点

出力しないADCカウントがある

- ➤ ADCのビットに対応する容量素子の容量が浮遊容量により増大

- 容量の比が 32:16:8:4:2:1 からずれている

- → 原因:容量素子の接続を切り替えるスイッチ

- → 容量に比例した個数のトランジスタをスイッチに使用することで 解決を試みた

#### 17

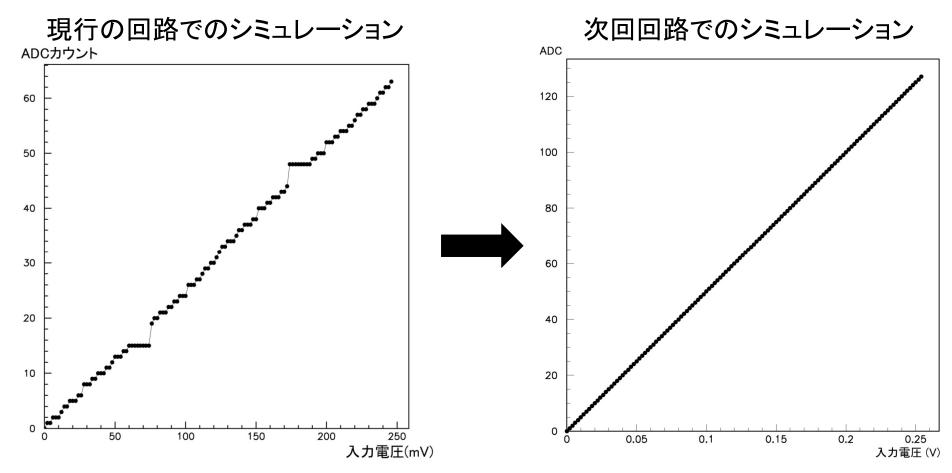

#### ADCのシミュレーション

・ プロセス情報なども含め詳細にADCのシミュレーションをおこなった

- ・ 再設計したADCではすべてのADCが出力した

- → 次回試作で出力しないADC問題の解決が見込める

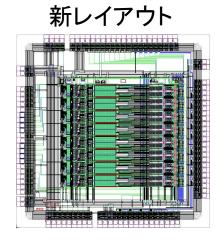

### Layout design

#### Layout design was completed.

$-0.35\mu m$  TSMC process  $\Rightarrow$  the same

- Chip size : 2.85 mm x 2.85 mm  $\Rightarrow$  4.3 mm x 4.3 mm

- # of pad :  $80 \Rightarrow 100$

- # of channel :  $8 \Rightarrow$  the same