# 高エネルギー加速器実験に向けた SOIPIX:PIXORの全体動作確認試験

東北大学大学院 素粒子実験研究室 修士1年 篠田 直幸

# 目次

- I. イントロ

- SOIPIXについて

- SOIPIXの崩壊点検出器への応用

- II. 高エネルギー実験へ向けた崩壊点検出器PIXORについて

- III. 試作機PIXOR1の試験状況

© Rey.Hori

# SOIPIX(SOI PIXel検出器)とは?

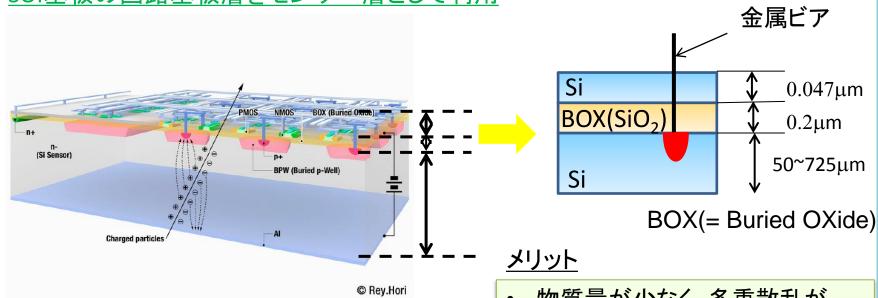

### SOI基板の回路基板層をセンサー層として利用

### SOIPIXの特徴

読み出し回路とセンサー層が一体化 →モノリシック型

回路層とセンサー層のBOX層による絶縁 →SOI CMOS構造

- 物質量が少なく、多重散乱が小さい

- センサー寄生容量が小さいので、 ノイズを小さくできる

- バンプボンディングがないので、 高い位置分解能が得られる (~10μm)

- 放射線耐性がある

## SOIPIXの放射線耐性

Single Event Effect

疑似信号を引き起こす 絶縁層により遮断 -> 耐性が高い

プロセスは終了-> 後は到着待ち・・

蓄積ホールによる下の閾値変動

→ 読み出し回路が正常動作しない

→現在、対策中・・

Si層を導入

- 蓄積ホールの影響を打ち消す

- クロストーク (センサー・回路間の干渉) の抑制

## SOIPIXの崩壊点検出器への応用

| 要求性能    | SOIPIXとの相性                                                  |

|---------|-------------------------------------------------------------|

| 高い位置分解能 | ○ SOI CMOSの導入: 有感面積を細かく区切れる( <u>10μm</u> )                  |

| 低い占有率   | ○ 空間的:ピクセルサイズの縮小化が可能                                        |

|         | 時間的: Chip-On-Sensor による、各ピクセル同時<br>読み出しが可能 -> <u>0.1%以下</u> |

| 低物質量    | O センサーの薄型化が可能(センサー厚 100 or 50μm)                            |

| 高速読み出し  | ○ 複雑なデジタル回路を搭載でき、<br>Hit情報のみを読み出せる(Intelligent)             |

| 放射線耐性   | △ SEE(単発現象)には強いが、TID(積算線量)に対しては<br>不十分 →対策が可能 (>10Mrad)     |

(Belle II へ向けてのパラメータ:目標)

Belle IIなどの次世代高エネルギー加速器実験において有望

## PIXORに行く前に・・

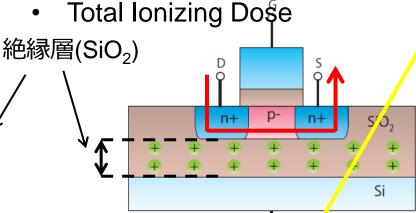

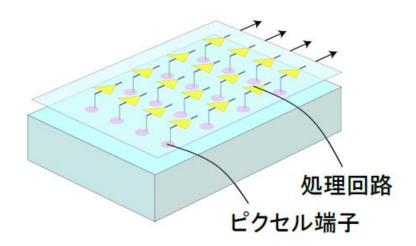

• Pixel型検出器(Chip-On-Sensorの場合)

- 1Pixelにつき一つの処理回路を搭載

- ▶ 高機能を追求すると…

- ■回路面積が増加⊗

- ➤ Pixel Sizeの増加

- 位置分解能の悪化⊗

この問題を解決するのが、PIXOR(ピクサー)です。

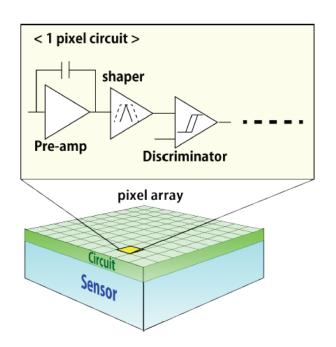

# PIXORのターゲット

Belle II SVD最内層(Layer3:r~38mm)へインストールを目指してます!

→物質量・占有率の更なる低下を狙う

• Belle II SVDのジオメトリ

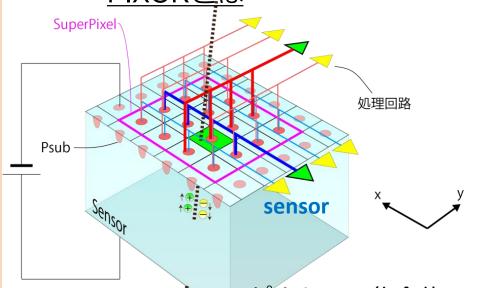

# PIXOR(PIXel OR)の開発 (東北大 D1小野さんが考案)

• PIXORとは

Super Pixe (n×nピクセルの集合体)

### 主な特徴

- 高い位置分解能

- Intelligentな回路機能 を併せ持つ理想的な検出器

#### 信号検出の流れ

- 1. Hit信号のX, Y方向への分離

- 2. Super Pixelの各列ごとに ORをとり、処理回路へ送る

•Pixel型に対するメリット

位置分解能が改善できる

(回路面積の減少 処理回路数:n² -> 2n)

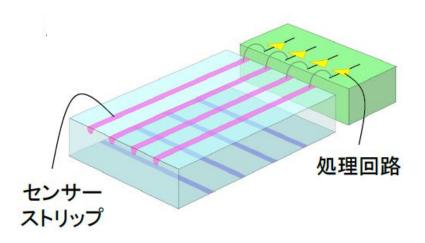

- •Stripに対するメリット

- ゴースト発生、占有率の低下

要求性能に応じてOR数を変更が可能! (位置分解能、回路面積、ゴーストヒットの低減、etc)

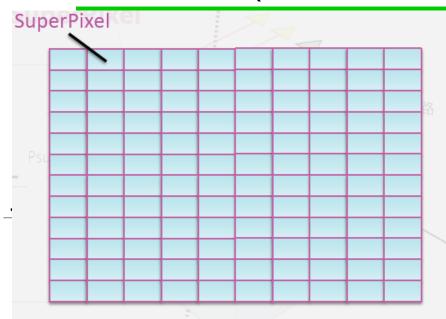

# PIXOR(PIXel OR)の開発

SuperPixelが並べられた構造

#### 主な特徴

- 高い位置分解能

- Intelligentな回路機能 を併せ持つ理想的な検出器

#### 信号検出の流れ

- 1. Hit信号のX, Y方向への分離

- 2. Super Pixelの各列ごとに ORをとり、処理回路へ送る

•Pixel型に対するメリット

位置分解能が改善できる

(回路面積の減少 処理回路数:n² -> 2n)

•Stripに対するメリット

ゴースト発生、占有率の低下

要求性能に応じてOR数を変更が可能! (位置分解能、回路面積、ゴーストヒットの低減、etc)

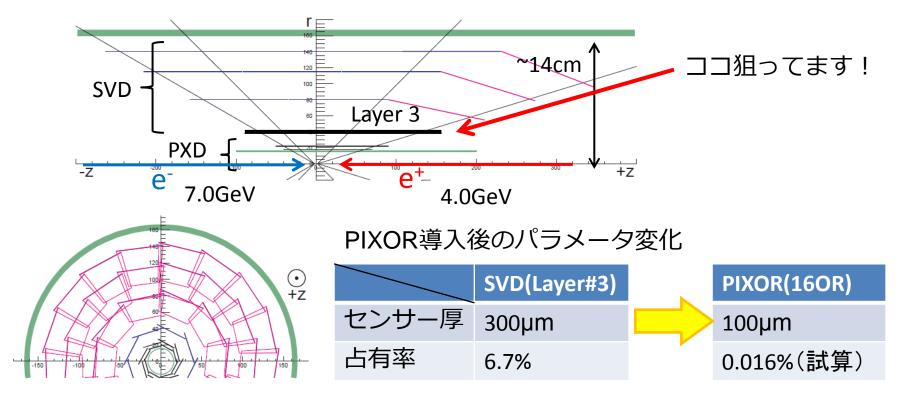

## PIXORの特徴

- PIXORのメリット

- PIXOR構造を用いることで位置分解能が改善する

- ▶ 回路面積が小さくなるので、より小さなピクセルを導入できる

- バイナリヒット判定

- ➤ 早期にHit情報を2値化し、大型のキャパシタが不要になり、 回路面積が縮小

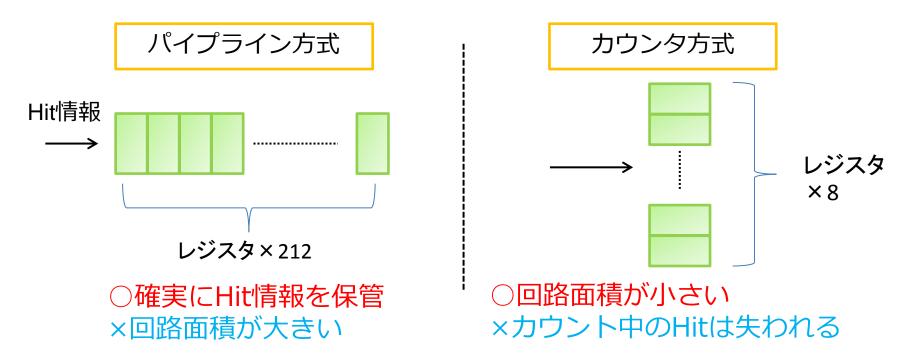

- バイナリカウンタによるトリガー待ち

- ➤ トリガー時間をカウンタで管理し、回路面積の縮小 PIXOR1のパラメータ

| Pixel Size       | φ : 25 z : 40 (μm)    |

|------------------|-----------------------|

| OR 数             | 16                    |

| Sampling rate    | 42.33MHz              |

| Trigger Latency  | 5 (μs)                |

| Point resolution | φ : 7.2 z : 11.5 (μm) |

### PIXOR1の開発・試験状況

- ➤ PIXOR1の評価項目

- 1. PIXOR処理の確認

- 2. デジタル回路の正常動作

- 3. PIXOR処理 + デジタル回路を通しての HIT信号確認

> 達成項目

デジタル回路の動作

- 本講演での内容

- Preamp + Shaperの出力確認 →PIXOR処理が正常に行われているか

- アナログ + デジタル回路の統合試験

- →PIXOR1全体の確認、Discriminatorの閾値を決定

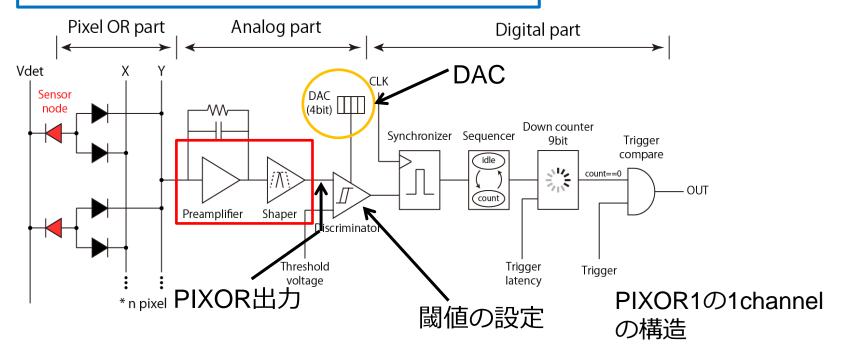

**XDiscriminator**

→ある一定の閾値を基準に、入力信号波形が Hitかどうかを判断

### PIXOR1の開発・試験状況

- ➤ PIXOR1の評価項目

- 1. PIXOR処理の確認

- 2. デジタル回路の正常動作

- 3. PIXOR処理 + デジタル回路を通しての HIT信号確認

> 達成項目

→ 正常動作確認 🙂

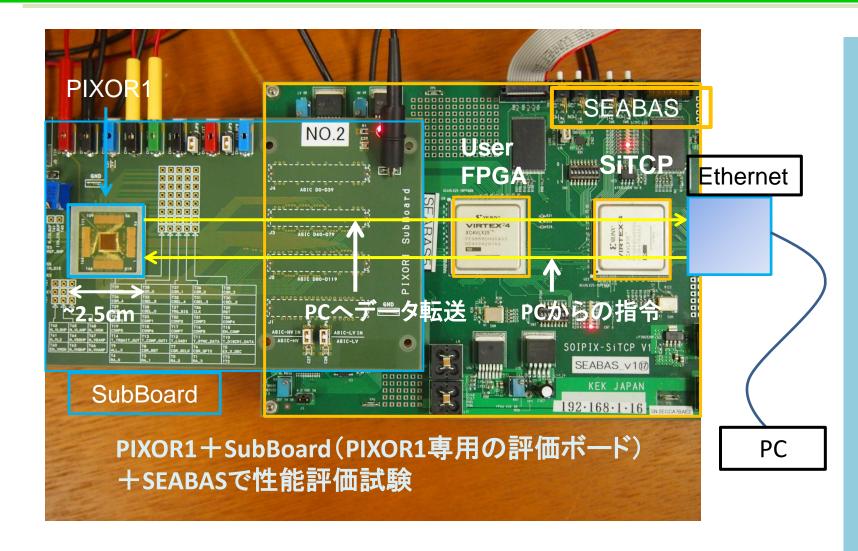

# PIXOR1の試験ボード

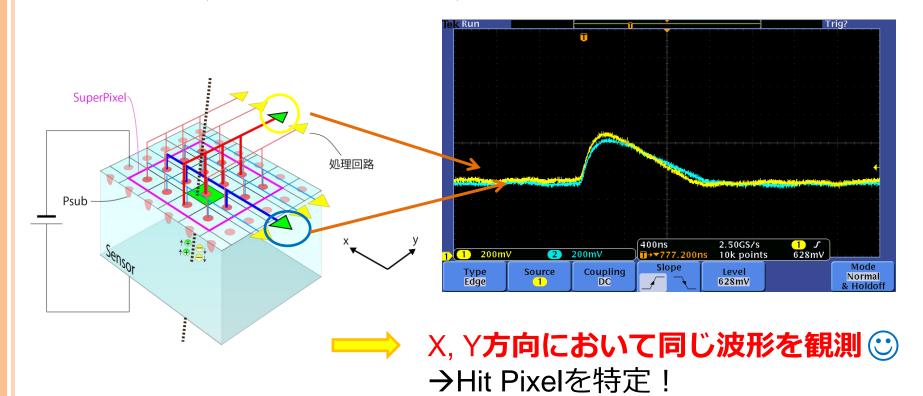

# PIXOR処理の確認

- PIXOR処理後のPreamp + Shaper出力を観測

- ▶ 二次元の位置情報を得るためにX, Y方向で同じ波形を出力する必要がある (使用線源: Cd-109)

# PIXOR1の全体動作確認試験に向けて

- ✓ PIXOR出力..OK! <sup>②</sup>

- ✓ デジタル回路も正常動作..OK! ☺

- ➤ 放射線源を用いたHit確認

- ▶ ビームテスト が出来るのでは??

- 各チャネルの閾値(ペデスタル 値)にバラつきがある→Hit判定がチャネル依存する

- ▶ 閾値を一定にし、均一なHit 判定が出来るように調節する (トリミングと言います)

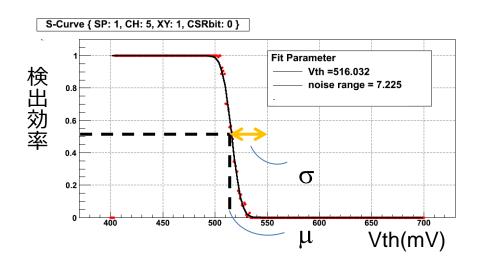

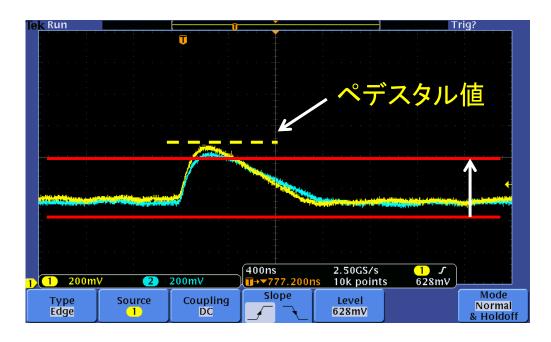

# ペデスタル値の測定

• 測定のフロー

Discriminatorの 閾値電圧変化

1000回トリガー

Hit判定数 カウント

Hit検出数 の変化

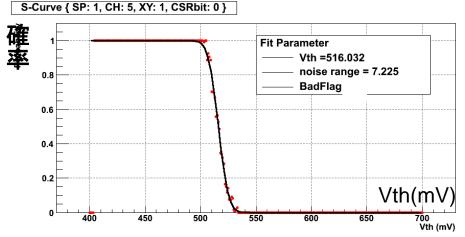

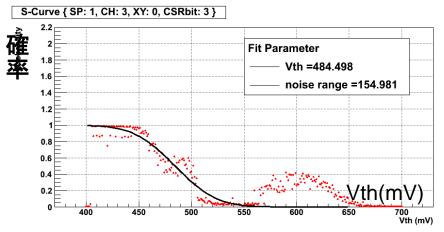

### ▶ S-Curveにより閾値電圧決定

- <u>S-Curveとは?</u> ディスクリにアナログ信号を入力 し、閾値を変化させその検出効率 をプロットしたもの

- 相補誤差関数による フィッティングで、

- 中心値 <sub>μ</sub>

- 幅σが求まる

# ペデスタル値の調整

- 一般にPixel型検出器では・・

- 4 各Pixelごとに細かく閾値を調整

→個性があるため

- 2. なるべく値を揃えた後に、チップ全体で一様な閾値を設定する

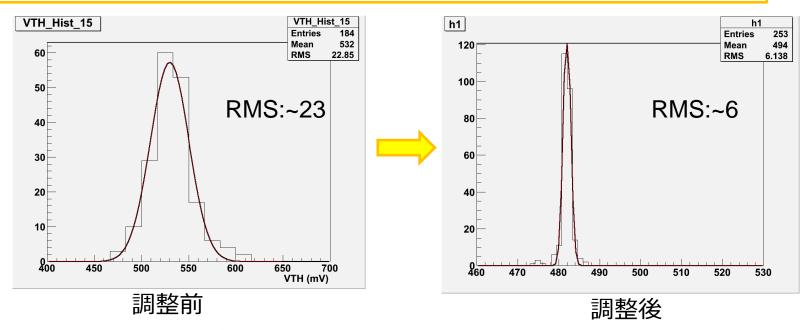

各チャネルのペデスタル値の分布を狭めることが出来た →ペデスタル値が一定になり、シグナルの確認を行いやすい

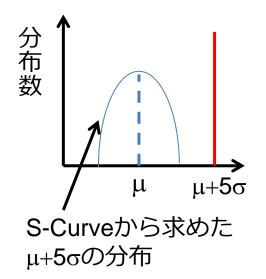

# Discriminator閾値設定

- 閾値決定までの流れ

- S-Curve測定により、各チャネルの μ+5σの値を求める

- チャネルごとのノイズを考慮

- 2. 各チャネルのμ+5σの分布を求め、チップ 全体のノイズを考慮した値を出す

- ➤ グローバルな閾値(PIXORの閾値)の決定

線源のみに応答し、ノイズを拾わない 閾値を決定する!

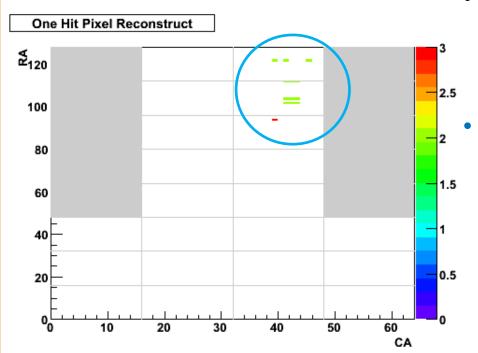

## Sr-90線源照射試験

- 動作CLK: 25MHz

- トリガーレート:200Hz

の条件下で10万イベントを取得

- 線源アリでHit Pixelの分布が見えた

→とりあえずHitは見えている!◎

- →第一段階クリアー

### Hitチャネルの分布がまばら…⊗

▶ V<sub>back</sub>により、うまくPreampが 機能していないチャネルがある → 再度、S-Curveを測定し 詳しく測定

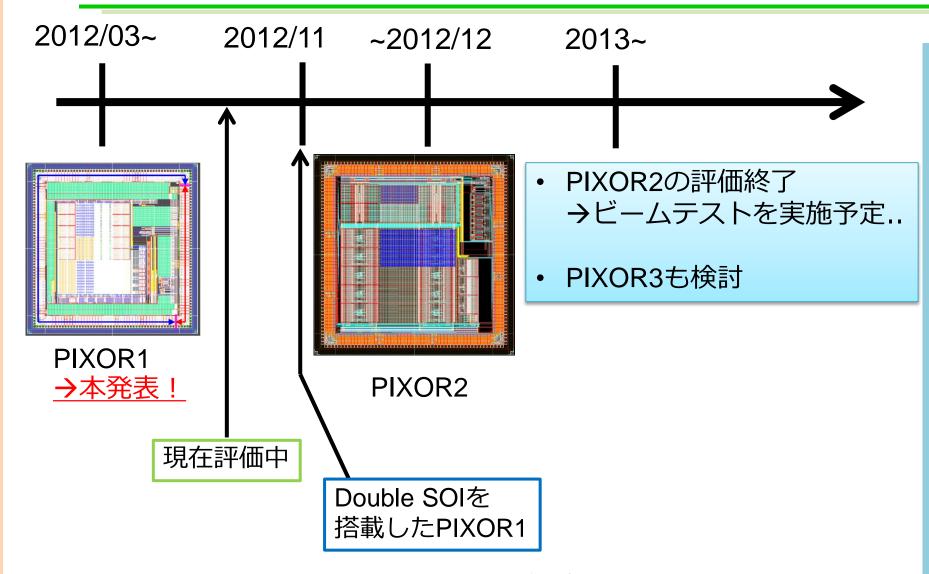

# PIXORの今後

# まとめと今後の予定

### > まとめ

- SOI技術を用いたPIXORを次世代の高エネルギー実験のための崩壊点検出器として開発

- 試作機PIXOR1の全体動作確認試験を行った

- ◆達成項目: PIXOR処理、アナログ+デジタル回路の一連の動作 Sr-90線源を用いたHITシグナルの確認

### ▶ 予定

- X線源(Cd-109)を用いての試験

- Double SOIによるクロストーク抑制の確認(11月~)

- 現時点での消費電力の見積もり(DEPFETは~0.1W/cm²)

# Back Up

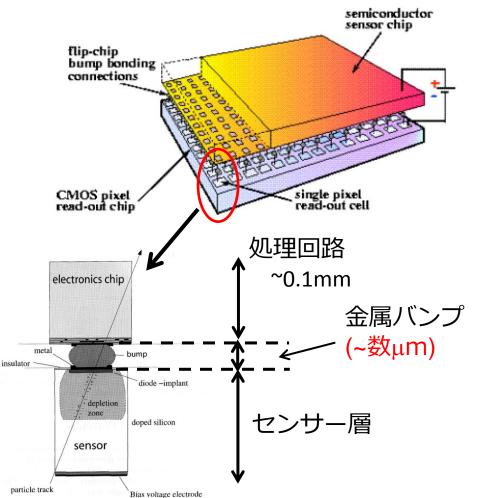

# ハイブリッド型検出器

■ センサー層と処理回路を個別に作り、金属バンプにより接合

- 検出器・エレキを別々に 作り金属バンプで接続

- 金属バンプのサイズによる 位置分解能の制限

- 余分な物質量が多い

- 寄生容量の増加による 処理スピードの低下

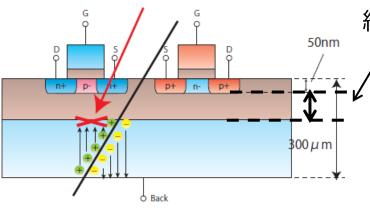

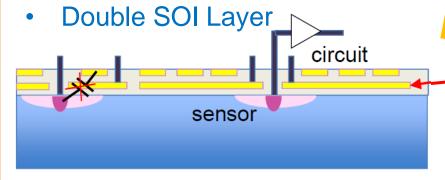

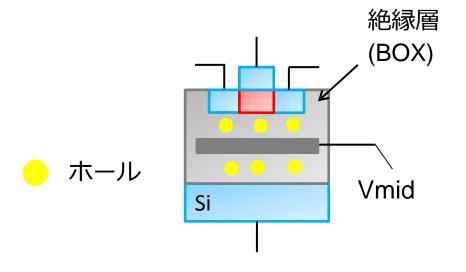

### Double SOIによる放射線対策

### • Double SOI構造

→絶縁層(SiO₂)に新たにもう一層のSiを導入することで、 トランジスタの閾値変動を防ぐ

蓄積したホールにより トランジスタ下面に電子が誘起 され、閾値電圧が負方向にシフト →読み出し回路が正常動作しない

絶縁層にSi層を導入し、負電圧を 印加することでホールを相殺

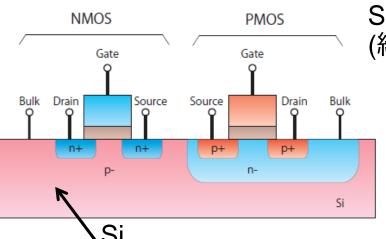

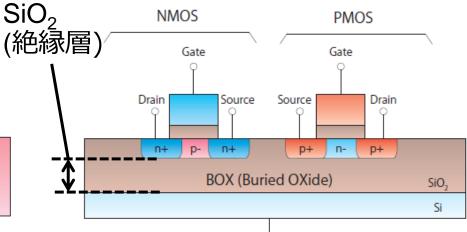

### Bulk CMOSとSOI CMOS

### Bulk CMOS

Si基板内にて、トランジスタを 作成している

#### SOI CMOS

各トランジスタ素学が絶縁層により仕切られている

### メリット

- ・ センサー寄生容量の低下

- > 高速動作、低消費電力

- 高集積化が可能

- 温度耐性がある

# Pixel型とStrip型検出器の比較

### Pixel型

### Strip型

### メリット

- 占有率(HitしたPixel数 / 全Pixel数) が小さい

- ゴースト発生なし

### デメリット

- 位置分解能に制限(Onセンサー)

- 読み出しに時間がかかる(Offセンサー)

### メリット

- 位置分解能が小さい

- 読み出し時間が短い

### デメリット

- 占有率が大きい

- ゴーストHitが発生

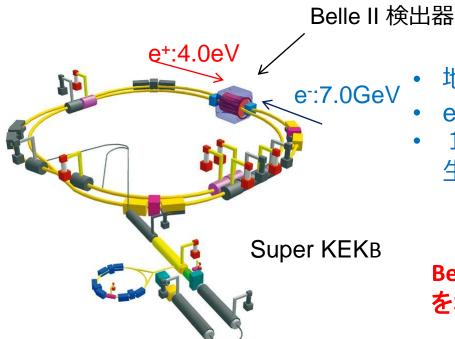

# Belle II実験

■B中間子を多量に生成し稀崩壊を精度よく測定し、 標準模型を超える物理の探索を行う

• 地下11m, 円周3kmの地下トンネル

• e+: 4.0GeV , e-: 7.0GeV

1秒間に800個のB中間子ペアを 生成(→Belle実験の40倍!)

Belle 実験の約10年分のデータ量をわずか3か月で収集できる

現在、アップグレード中 → 2015年実験開始予定 (物理runは2016年から)

### カウンタによるトリガー待ち

・ ヒットした信号はすぐに出力されない

→データ信号の合図はヒット時間から一定時間後に届く (その間データの保管が必要)

※Belle II のsampling rate:42.33MHzでTrigger latency 212CLK(5μs)の場合

# PIXOR処理

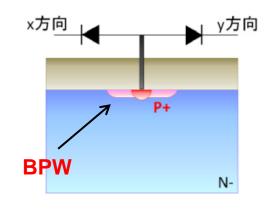

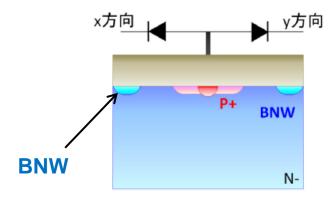

- 2-diode構造

- ➤ 二つのダイオードにより、センサーからの信号を均等に二 方向へ分ける

#### 2-diodeA

#### 2-diodeB

#### BPW, BNW:

電荷収集速度を上げるための 濃いP型、N型半導体

# PIXOR1デジタル回路

- Synchronizer

- ➤ 入力信号を動作CLKに同期させ、1CLKに整形する

- SEQ(Sequencer)

- ➤ カウンタの使用状況を判断し、Hit信号をカウンタへ送る

- Hit Time Counter

- ➤ トリガー時間Hit情報を格納し、カウンタの値が9'b1で Enable信号を生成し、外部TRGとの一致でHitと認識

### S-Curveによる測定

- S-Curveによるフィッティング

- ➤ VthをShaper出力のbaseline付近から振幅が最大となる値 まで変化させ、その最大値となる点を測定(ペデスタル値)

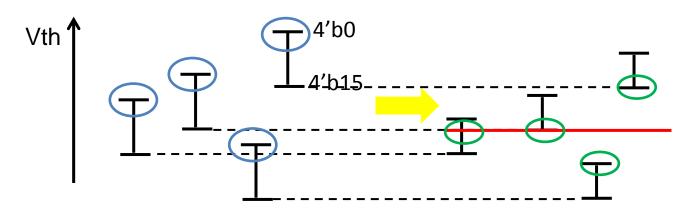

## 補正用DACを用いた閾値調整

各チャネルの閾値を揃える

### ◆閾値調整の手順

- I. 補正bitの変化幅を調整し、 変化幅を最小に

- II. 4'b0のmax, 4'b15のmin の中間の値を揃える値にした

- III. 各チャネル、補正用DACを用いて 上の値に調整

調整前に比べ、閾値の分布幅が小さくなった →ちゃんと補正用DACを調整出来 ている(スライド13の上の図)

# ③DACを用いたDiscriminator閾値調整

### S-Curveによる測定

各チャネルのペデスタルでノイズを 拾う確率は1/2

- →この時の電圧を各チャネルでの ペデスタルとする

- ▶ 相補誤差関数でフィットし、 ペデスタル値+ノイズ値を決定

相補誤差関数 erfc(x) =  $\frac{2}{\sqrt{\pi}} \int_{x}^{\infty} e^{-t^2} dt$  (Gauss関数の積分)

\* 正常なS-Curveの振舞いをしていないチャネルはノイズレベル 測定の対象外とした →Bad Channel

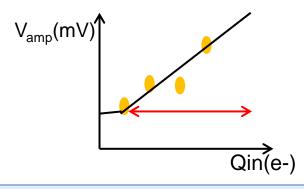

# ゲインの測定

- 複数の入力電荷に対応するTest Pulseを入力

- それぞれをS-CurveによりFittingし、V<sub>amp</sub>を得る

- ▶ 各チャネルごとにQinに対するV<sub>amp</sub>の変化をFitする

Qinの増加に比例してV<sub>amp</sub>は増加 -> Gain = V<sub>amp</sub>/Qin 増加部分の最小値をそのチャネル でのQinとする

V<sub>amp</sub> :shaper出力の振幅

### 各チャネルでのGain, Qinが求まった

- ▶ ヒストグラムを作成し、

- I. ノイズ分離のために(シグナルがノイズに埋もれない)入力すべきQin

- II. 大面積TEGにおける**Gain** が求まる