修士論文

ILC衝突点モニター用

ピクセル検出器読み出し回路の設計開発

東北大學大学院理学研究科

物理学専攻

横山康博

平成 18 年

## 概要

現在計画されている ILC ( International Linear Collider ) 実験計画は, 重心エネルギーが TeV 領域にまで到達する電子・陽電子衝突型加速器実験である. ILC の電子又は陽電子のビームは 0.87ms の長さを持つパンチトレインが 5Hz, つまり約 200ms 間隔で衝突を繰り返す. そのトレインは 307.7ns 間隔, 計 2820 のパンチから構成されている. これらの衝突によって対生成した電子ないし陽電子ビームの空間的, 及び時間的分布から衝突点におけるビームサイズを割り出し, 衝突条件の最適化に資することが Pair Monitor の目的である. そして, 本研究の目的は Pair Monitor の読み出し回路がビーム構造から要求される時間分解能, 感度, 雑音レベルを明確にした上で, その要求を満たす回路の開発を行うことである. そのために行う主な研究は, 回路シミュレータを用いた回路設計・評価とその試作チップに対する評価試験である. 本研究回路はアナログ・デジタル混載回路であり, 設計段階において, アナログ回路部には SPICE シミュレーションを, デジタル回路部には verilog シミュレーションを用いた評価試験を行い性能要求を満たす回路設計を行う. また, 試作チップの評価試験ではシミュレーション結果の再現を期待したが, コントロールレジスタ部において不具合動作を確認し, EB ( Electron Beam ) テスト・FIB ( Focused Ion Beam ) 加工により不具合個所の特定・回路内部の修正を行っている.

なお, 本研究回路の原案は JAXA の池田教授の発案によるものであり, 東北大学では, その回路のシミュレーションによる評価, 及び修正を行った. また, 本研究回路の試作時においては, レイアウト設計を(株)デジアン・テクノロジー社に依頼し, 試作製造は MOSIS に依頼した. 製造された試作チップの評価試験は東北大学において行った. 東北大学での研究は橋本健太郎君と共同で行われ, 回路設計・評価, 及びその試作チップに対する評価試験を行った. 本論文においては回路設計・評価の詳細を述べ, 試作チップに対する評価試験については簡単に述べることとする. 試作チップに対する評価試験についての詳述は橋本健太郎君による論文 [20] にある.

# 目 次

|                                       |           |

|---------------------------------------|-----------|

| <b>第 1 章 序論</b>                       | <b>9</b>  |

| 1.1 ILC 実験計画                          | 9         |

| 1.2 ILC が挑戦する物理                       | 11        |

| 1.2.1 Higgs study                     | 11        |

| 1.2.2 Supersymmetry                   | 12        |

| 1.2.3 Top Quark Study                 | 13        |

| 1.3 ILC の構成                           | 14        |

| 1.4 ILC 検出器の概要                        | 15        |

| 1.4.1 崩壊点検出器 (VTX)                    | 16        |

| 1.4.2 中間飛跡検出器 (SIT)                   | 17        |

| 1.4.3 タイムプロジェクションチェンバー (TPC)          | 17        |

| 1.4.4 カロリメータ                          | 18        |

| 1.4.5 $\mu$ 粒子検出器                     | 19        |

| 1.5 ビームプロファイル                         | 19        |

| <b>第 2 章 Pair Monitor</b>             | <b>20</b> |

| 2.1 Pair Monitor の原理                  | 20        |

| 2.1.1 $e^+e^-$ ペアが電磁場から受ける力の導出        | 21        |

| 2.1.2 Pair Monitor 上での $e^+e^-$ ペアの分布 | 22        |

| 2.1.3 $\sigma_x$ の導出                  | 24        |

| 2.1.4 $\sigma_y$ の導出                  | 24        |

| 2.2 3D シリコンピクセルセンサー                   | 26        |

| 2.3 読み出し回路                            | 27        |

| <b>第 3 章 回路設計</b>                     | <b>28</b> |

| 3.1 回路の製作目的                           | 28        |

| 3.2 回路概観                              | 33        |

| 3.3 ピクセルごとの回路構成                       | 35        |

| 3.4 アナログ回路部の構成                        | 36        |

| 3.4.1 CHAIN1 回路                       | 37        |

| 3.4.2 アナログ制御回路                        | 42        |

| 3.4.3 モニタ回路                           | 45        |

| 3.5 ディジタル回路の構成                        | 47        |

| 3.5.1 COUNT8 回路                       | 48        |

| 3.5.2 REGBNK4 回路                      | 49        |

| 3.5.3 DEC2B 回路                        | 51        |

|                                          |            |

|------------------------------------------|------------|

| 3.5.4 DEC2N 回路                           | 52         |

| 3.6 Glue 回路の構成                           | 53         |

| 3.6.1 CAPO 回路                            | 54         |

| 3.6.2 CAPB 回路                            | 55         |

| 3.6.3 CAPXY 回路                           | 56         |

| 3.6.4 CAPT 回路                            | 58         |

| 3.6.5 CAPL 回路                            | 60         |

| <b>第 4 章 回路シミュレーションを用いた評価試験</b>          | <b>62</b>  |

| 4.1 シミュレーションの手法                          | 62         |

| 4.2 アナログ部                                | 63         |

| 4.2.1 skew テスト                           | 67         |

| 4.2.2 温度テスト                              | 67         |

| 4.2.3 電子雑音テスト                            | 70         |

| 4.2.4 電源電圧のゆれに対する感度                      | 73         |

| 4.3 Pair Monitor のバックグラウンド処理のためのシミュレーション | 75         |

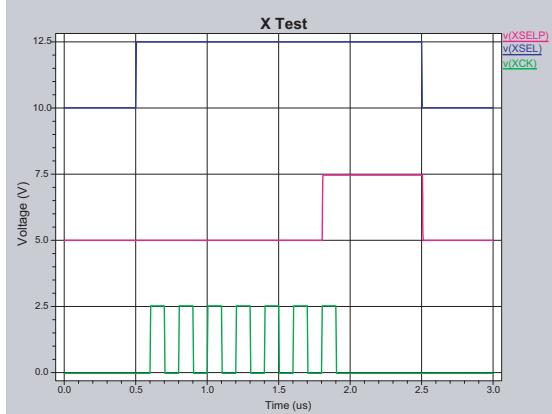

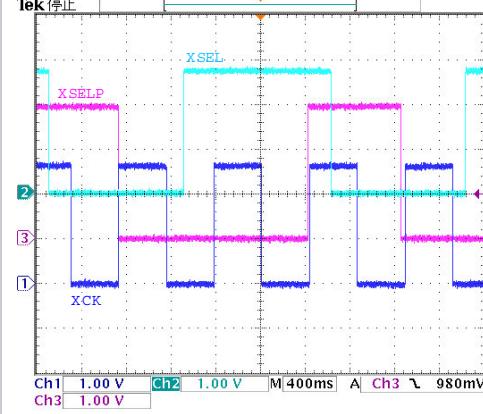

| 4.4 デジタル部                                | 76         |

| 4.4.1 verilog シミュレーション                   | 76         |

| <b>第 5 章 チップ製作</b>                       | <b>78</b>  |

| 5.1 チップ製作のプロセス                           | 78         |

| 5.2 レイアウト, デバイス設計                        | 79         |

| 5.3 レイアウト検証作業                            | 79         |

| 5.4 チップ製造                                | 80         |

| <b>第 6 章 評価試験</b>                        | <b>81</b>  |

| 6.1 チップ試験のためのシステム                        | 82         |

| 6.2 評価方法, 及びその結果                         | 82         |

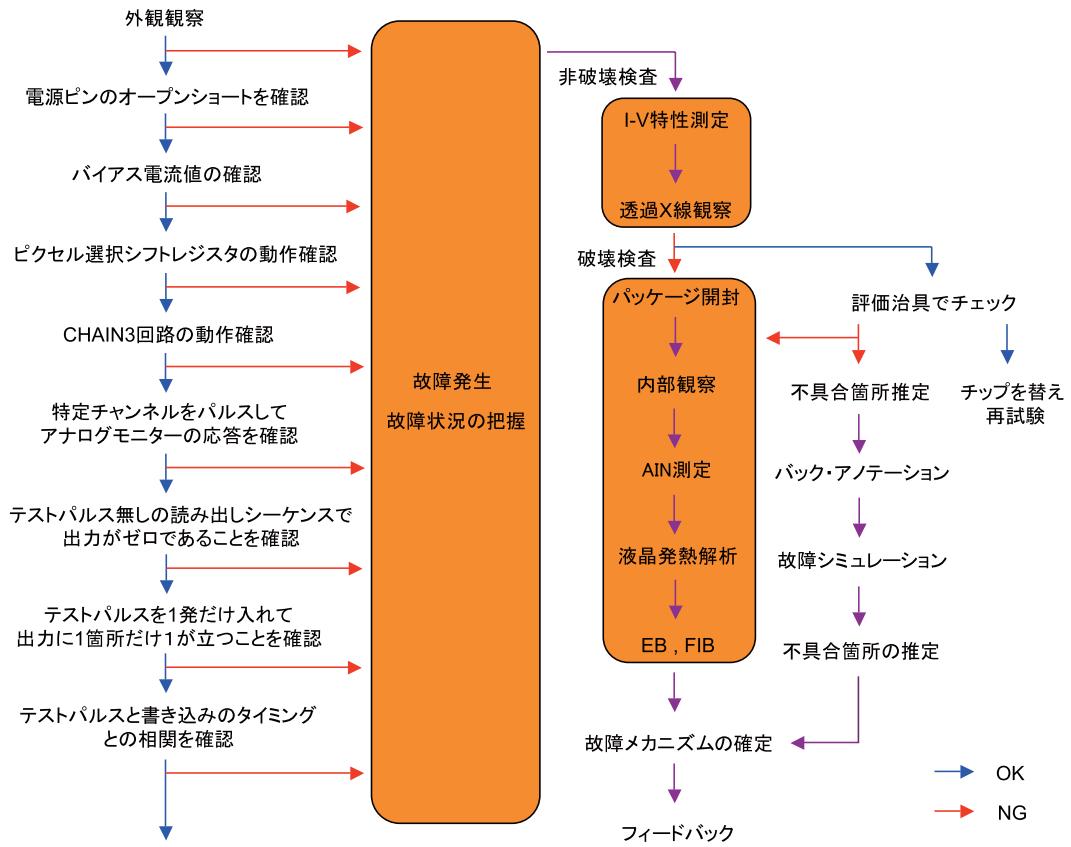

| 6.3 故障解析                                 | 84         |

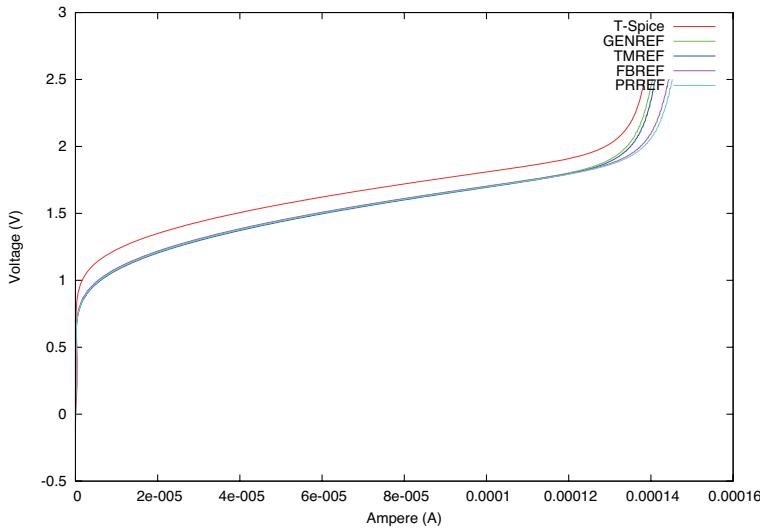

| 6.3.1 非破壊検査                              | 84         |

| 6.3.2 破壊検査                               | 85         |

| <b>第 7 章 結論</b>                          | <b>91</b>  |

| 7.1 まとめ                                  | 91         |

| 7.2 今後について                               | 92         |

| <b>付 錄 A 電子雑音</b>                        | <b>94</b>  |

| <b>付 錄 B チップのピン配置</b>                    | <b>95</b>  |

| <b>付 錄 C デジタル回路の波形</b>                   | <b>100</b> |

| <b>参考文献</b>                              | <b>103</b> |

# 図 目 次

|      |                                   |    |

|------|-----------------------------------|----|

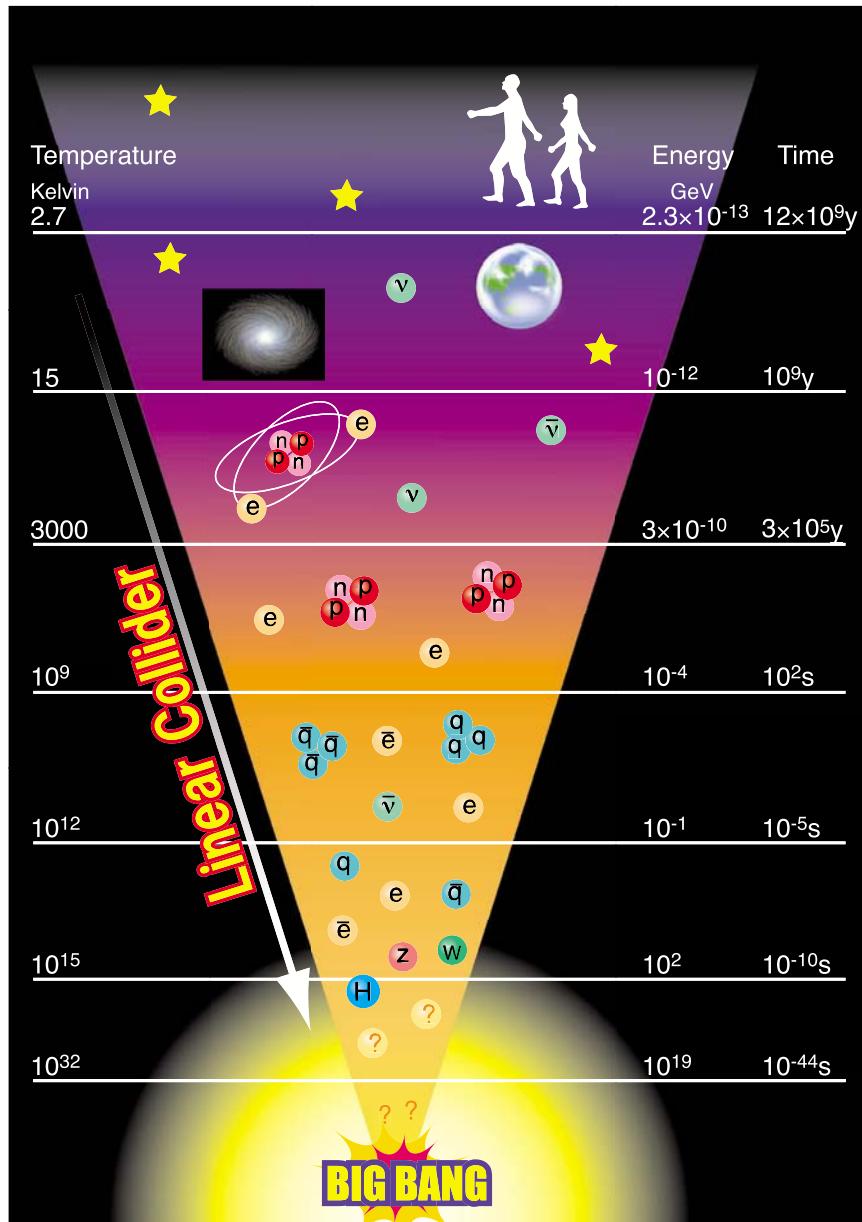

| 1.1  | 初期の宇宙のエネルギーと温度                    | 10 |

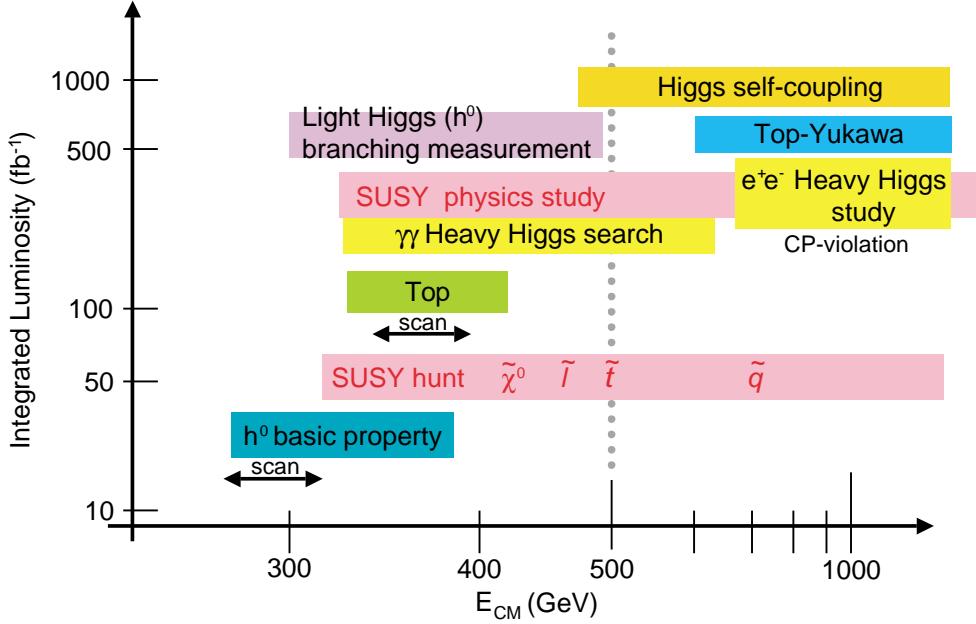

| 1.2  | ILC での物理のターゲットと重心エネルギー            | 11 |

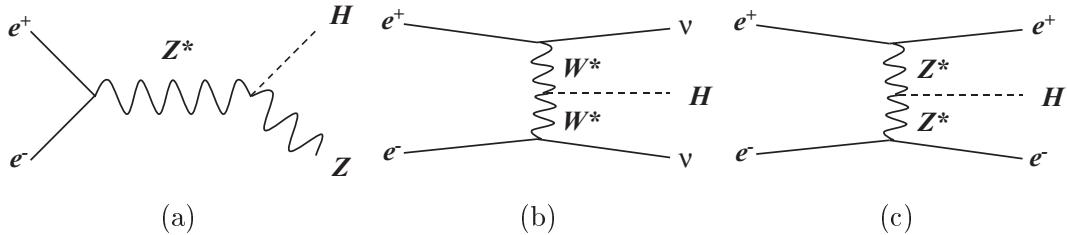

| 1.3  | ヒッグス粒子の探索に用いられる反応                 | 12 |

| 1.4  | ILC の概念図                          | 14 |

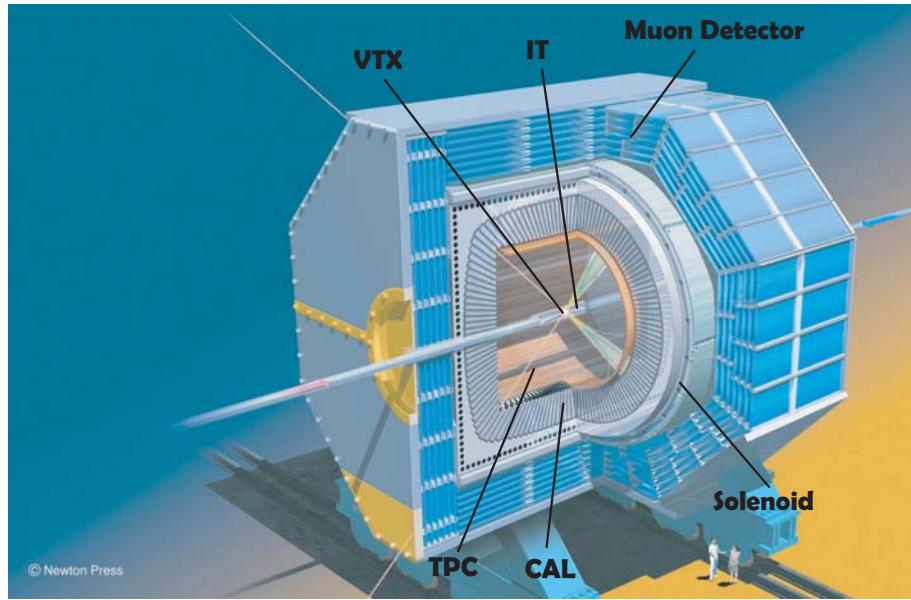

| 1.5  | GLD 検出器の外観 n                      | 15 |

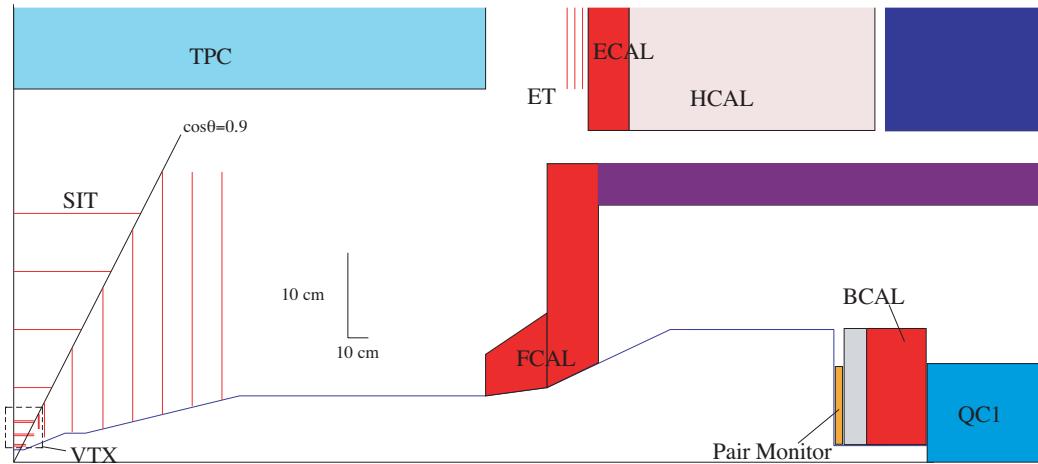

| 1.6  | 各検出器の位置関係                         | 16 |

| 1.7  | 崩壊点検出器の構造図                        | 16 |

| 1.8  | 中間飛跡検出器の構造図                       | 17 |

| 1.9  | 電磁力カロリメータの構造図                     | 18 |

| 1.10 | ハドロンカロリメータの構造図                    | 18 |

| 2.1  | Pair Monitor (左) とその構成要素 (右) [16] | 20 |

| 2.2  | ビームの電磁場による $e^+e^-$ の散乱 [6]       | 21 |

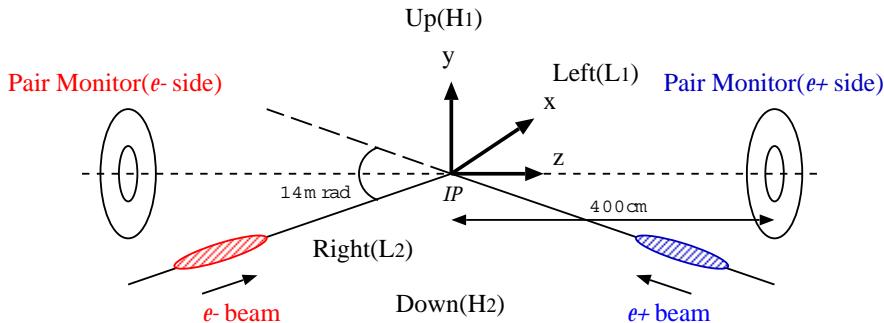

| 2.3  | ビームの座標系 [16]                      | 22 |

| 2.4  | Pair Monitor 上での衝突位置              | 23 |

| 2.5  | 衝突位置の分布                           | 24 |

| 2.6  | 衝突位置半径に対するエネルギーの分布                | 24 |

| 2.7  | IP での散乱角分布                        | 25 |

| 2.8  | Pair Monitor 上の方位角分布              | 25 |

| 2.9  | アスペクト比に対 $R$ に対する $R_{pv}$        | 25 |

| 2.10 | 3D ピクセルセンサー [9]                   | 26 |

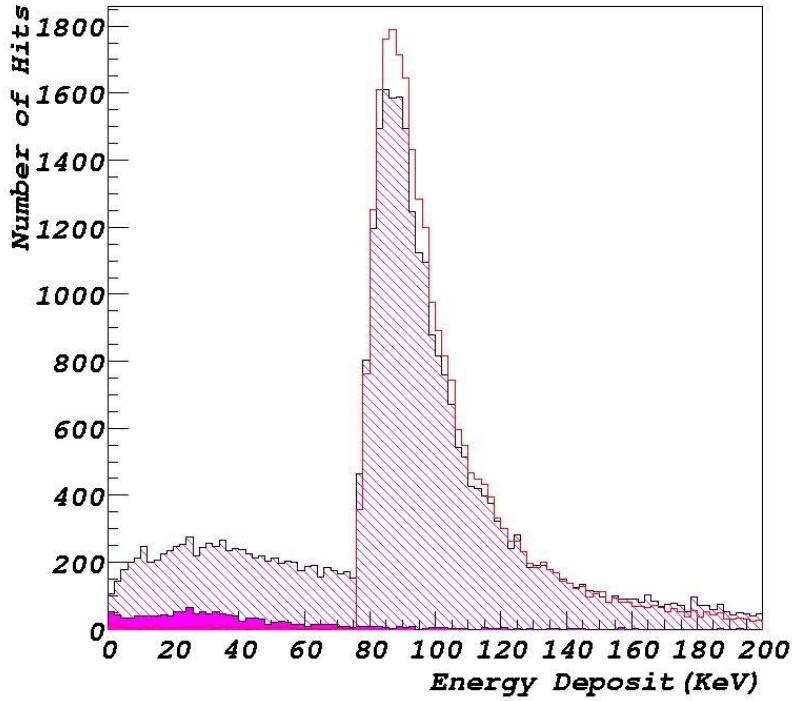

| 2.11 | Pair Monitor でのエネルギー・デポジットの分布     | 27 |

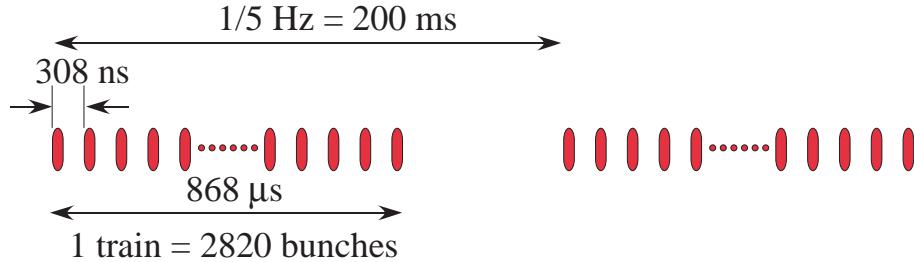

| 3.1  | ILC におけるビーム構造                     | 28 |

| 3.2  | 前研究回路の模式図                         | 29 |

| 3.3  | 本研究回路の模式図                         | 30 |

| 3.4  | 前研究回路の波形の 4 点サンプル                 | 31 |

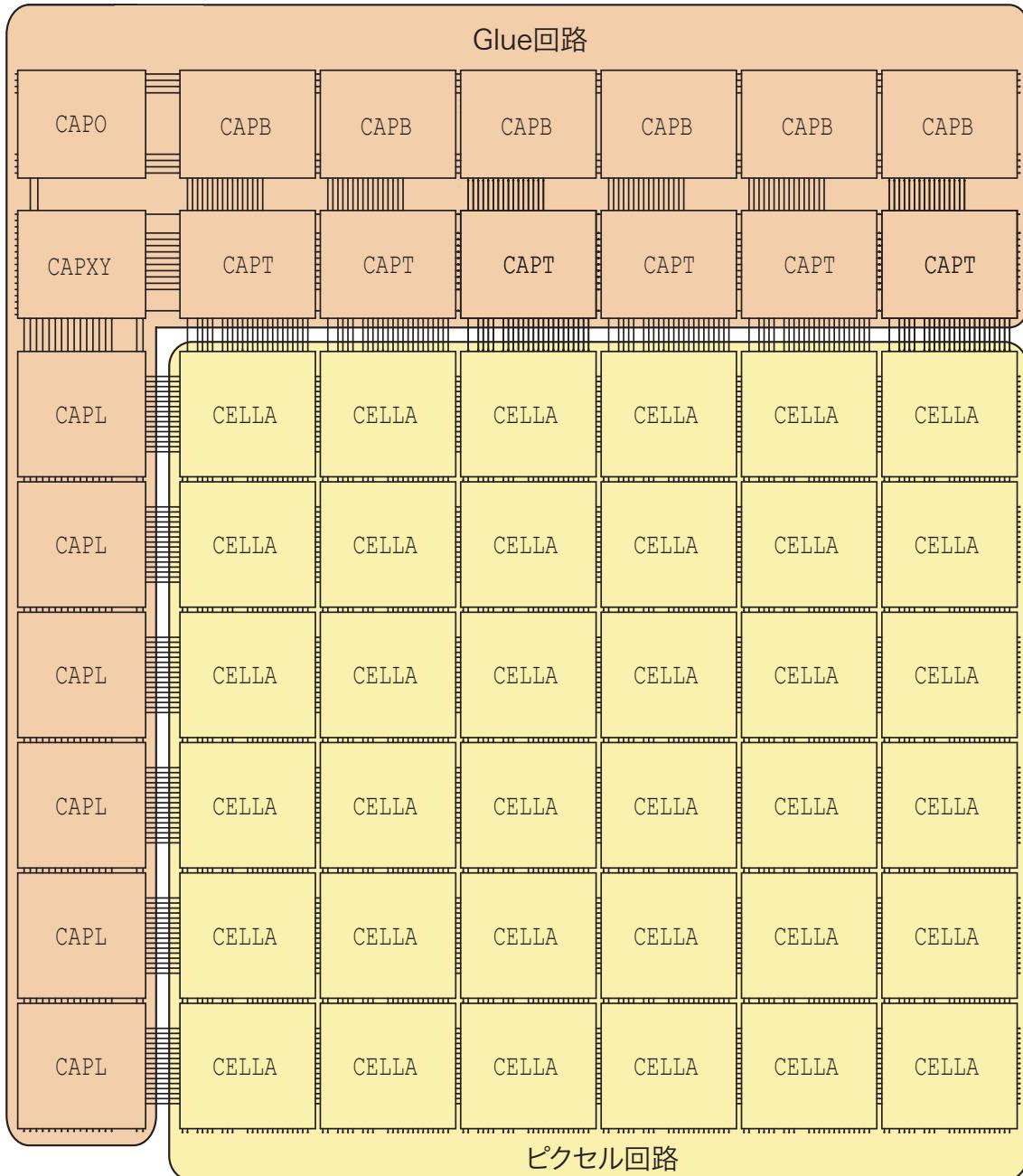

| 3.5  | 回路概観                              | 33 |

| 3.6  | 回路の階層構造                           | 34 |

| 3.7  | ピクセルごとの回路構成                       | 35 |

| 3.8  | アナログ回路部の構成                        | 36 |

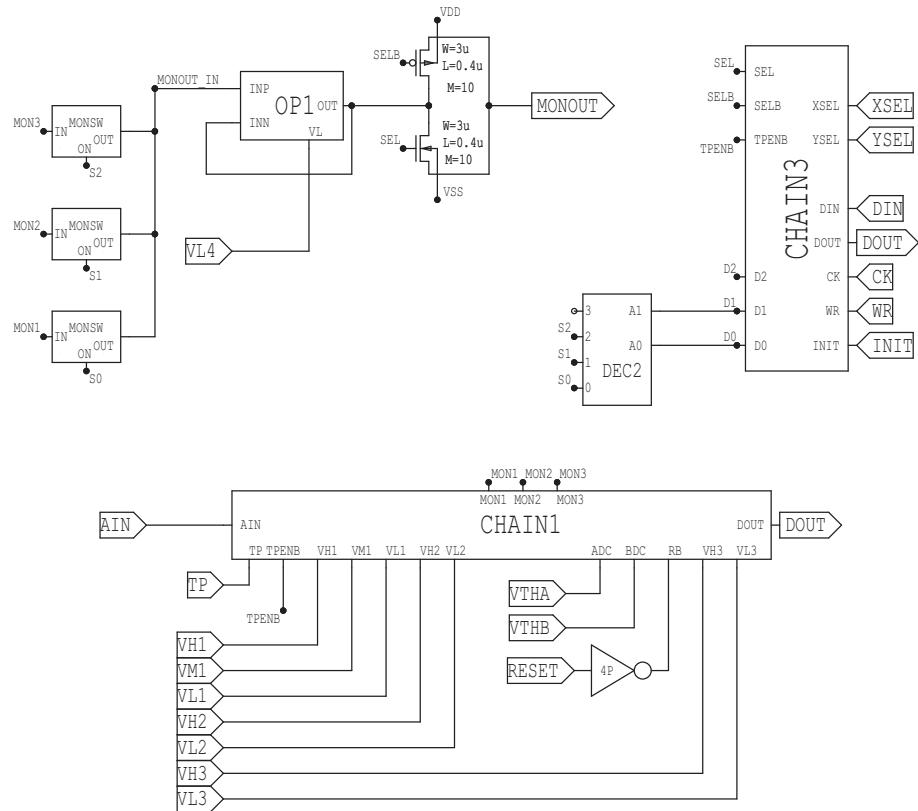

| 3.9  | CHAIN1 回路のシンボル (上) とその内部構成 (下)    | 37 |

| 3.10 | 前置増幅回路サブブロック                      | 38 |

| 3.11 | 前置増幅回路の入力信号                       | 39 |

| 3.12 | 前置増幅回路の入力信号と出力信号                  | 39 |

| 3.13 | 差動増幅回路サブブロック                      | 40 |

|                                             |    |

|---------------------------------------------|----|

| 3.14 差動増幅回路の出力信号とそれらの差をとった波形                | 40 |

| 3.15 コンパレータ回路サブブロック                         | 41 |

| 3.16 コンパレータ回路の出力信号と差動増幅回路からの出力の差をとった波形      | 41 |

| 3.17 アナログ制御回路                               | 42 |

| 3.18 CHAIN3 回路のシンボル(左)とその内部構成(右)            | 43 |

| 3.19 DEC2 回路のシンボル(左)とその内部構成(右)              | 44 |

| 3.20 モニタ回路                                  | 45 |

| 3.21 MON1 出力波形モニタ用信号                        | 46 |

| 3.22 モニタ回路で MON1 の波形を観測                     | 46 |

| 3.23 MON2 出力波形モニタ用信号                        | 46 |

| 3.24 モニタ回路で MON2 の波形を観測                     | 46 |

| 3.25 MON3 出力波形モニタ用信号                        | 46 |

| 3.26 モニタ回路で MON3 の波形を観測                     | 46 |

| 3.27 ディジタル回路の構成                             | 47 |

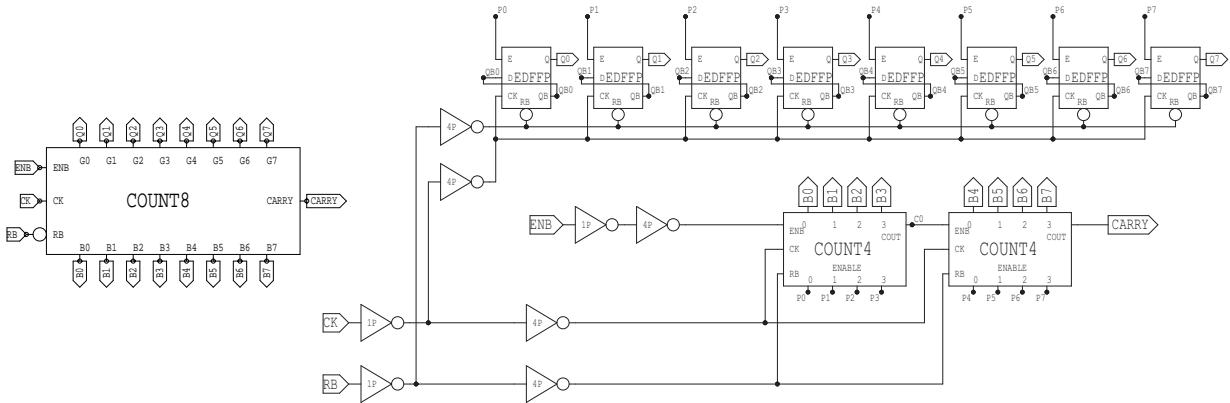

| 3.28 COUNT8 回路のシンボル(左)とその内部構成(右)            | 48 |

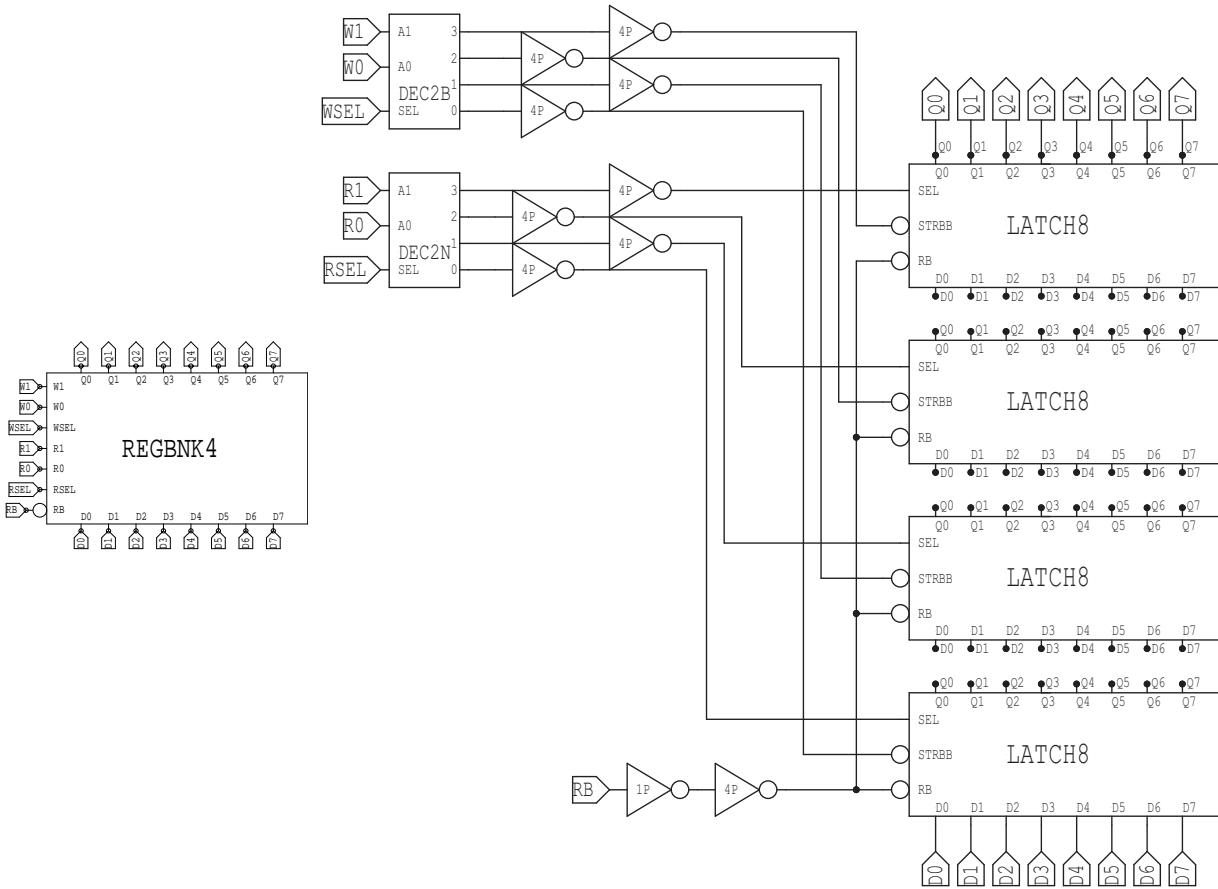

| 3.29 REGBNK4 回路のシンボル(左)とその内部構成(右)           | 50 |

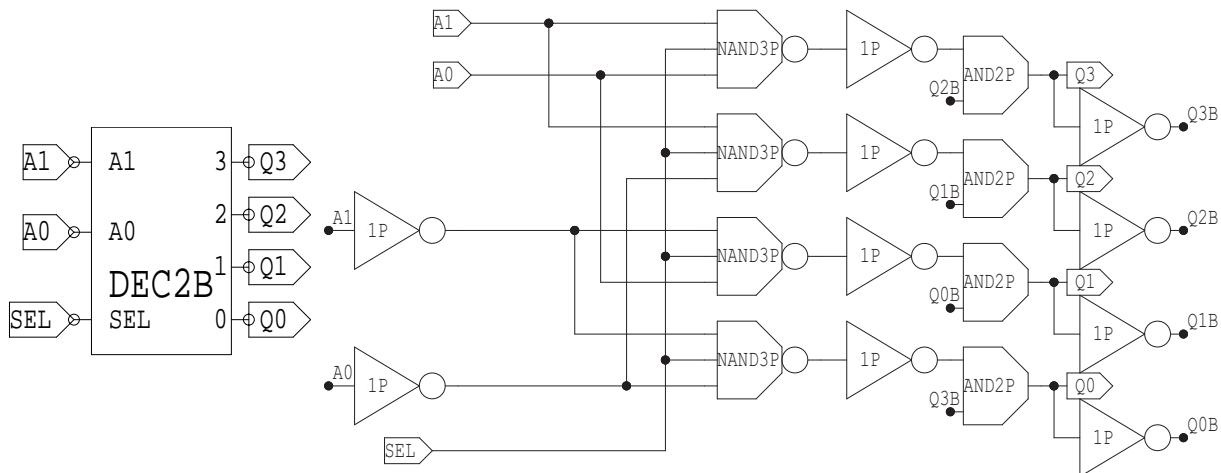

| 3.30 DEC2B 回路のシンボル(左)とその内部構成(右)             | 51 |

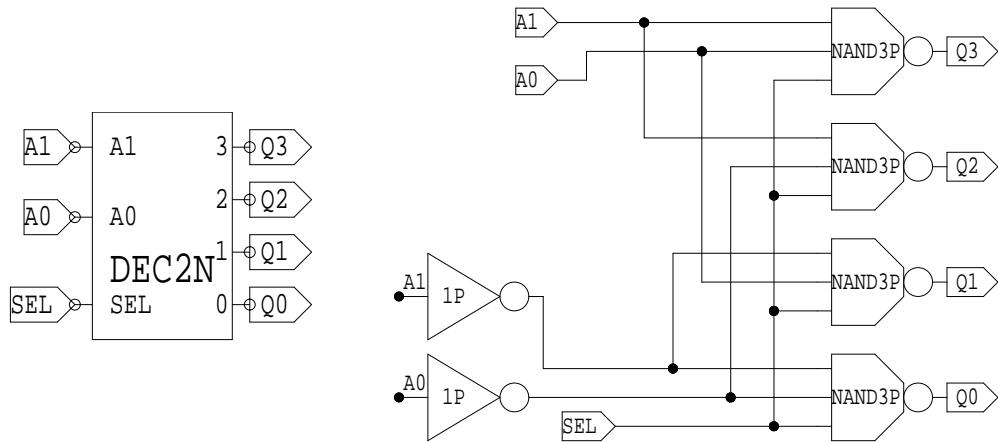

| 3.31 DEC2N 回路のシンボル(左)とその内部構成(右)             | 52 |

| 3.32 Glue 回路の構成                             | 53 |

| 3.33 CAPO 回路のシンボル(左)とその内部構成(右)              | 54 |

| 3.34 CAPB 回路のシンボル(左)とその内部構成(右)              | 55 |

| 3.35 CAPXY 回路のシンボル                          | 56 |

| 3.36 CAPXY 回路のシンボル(左)とその内部構成(右)             | 56 |

| 3.37 CAPT 回路のシンボル(左)とその内部構成(右)              | 58 |

| 3.38 CAPL 回路のシンボル(左)とその内部構成(右)              | 60 |

| <br>4.1 アナログ部の評価用回路図                        | 63 |

| 4.2 アナログ部の評価テスト                             | 65 |

| 4.3 モニタ回路で MON1 の波形を観測                      | 65 |

| 4.4 モニタ回路で MON2 の波形を観測                      | 66 |

| 4.5 モニタ回路で MON3 の波形を観測                      | 66 |

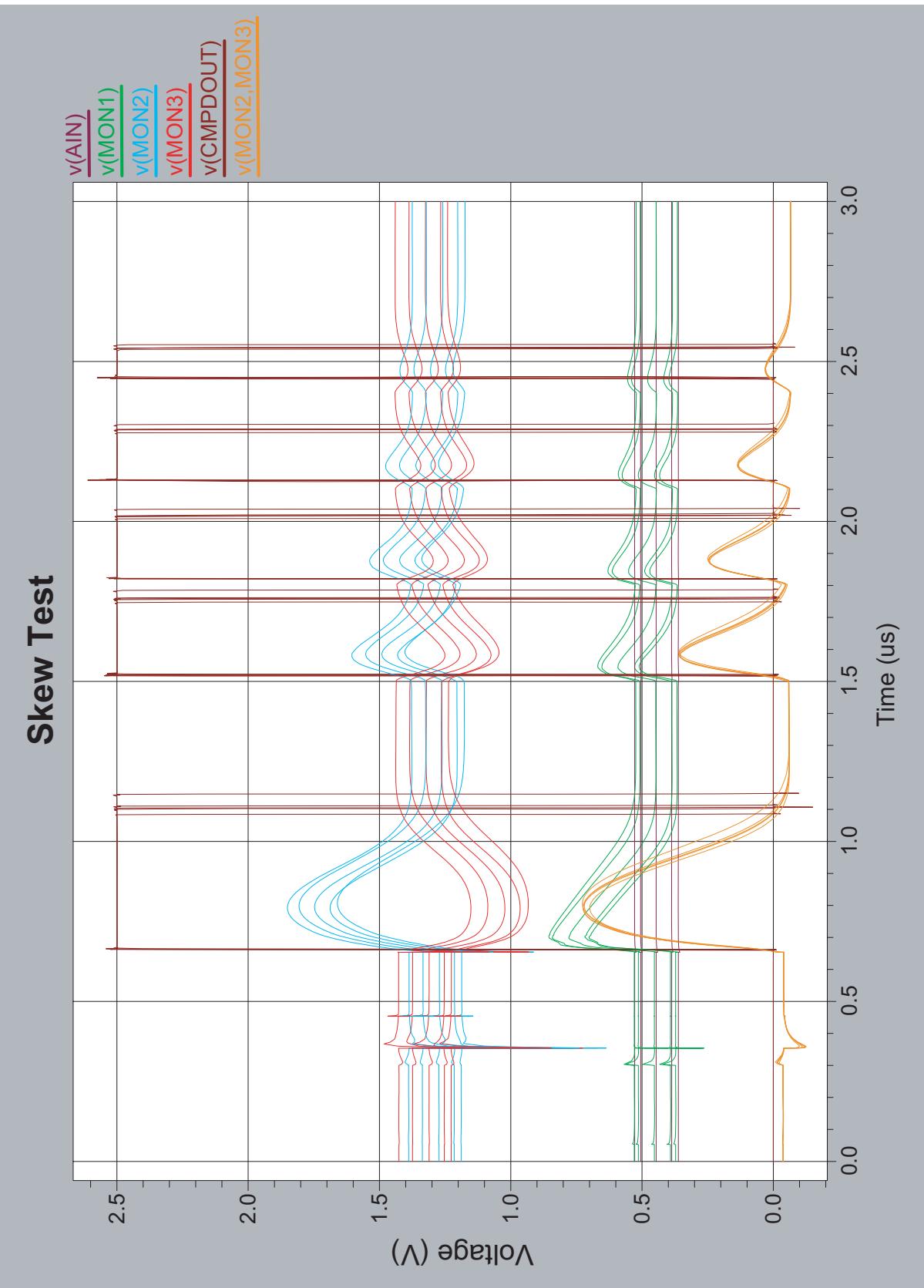

| 4.6 Skew テスト                                | 68 |

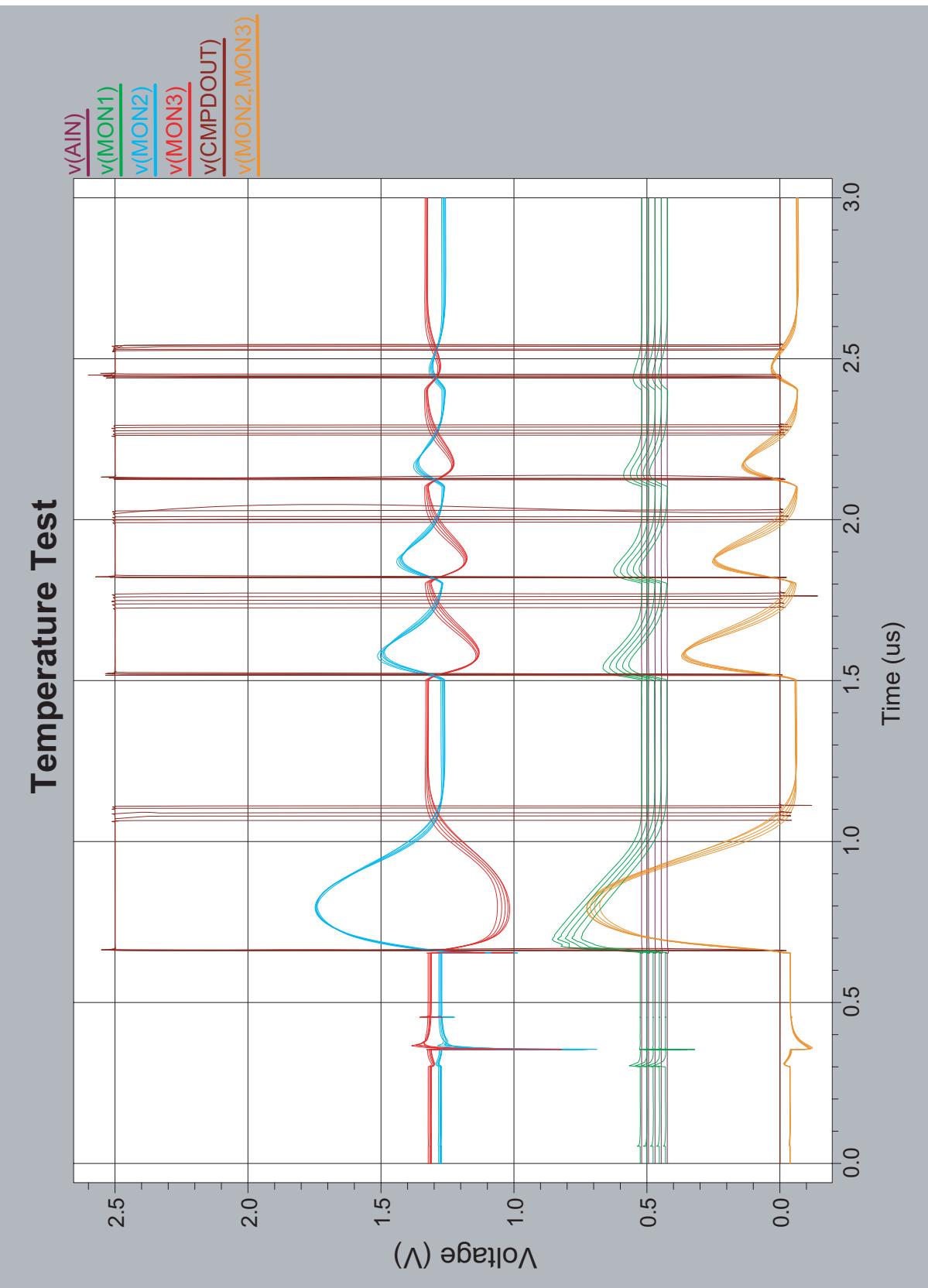

| 4.7 温度テスト                                   | 69 |

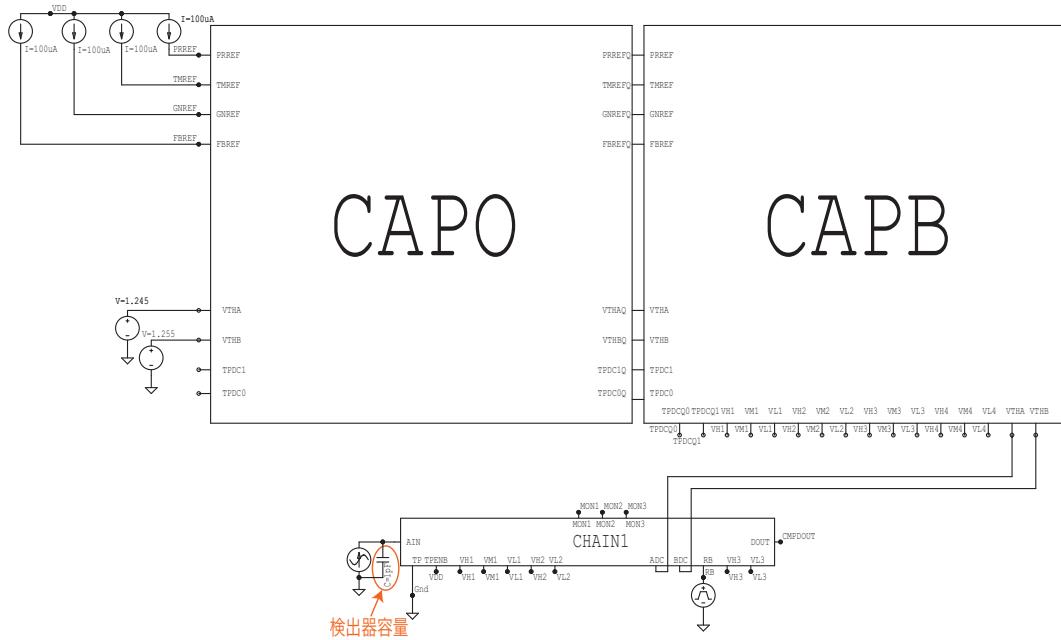

| 4.8 電子雑音評価用セットアップ                           | 70 |

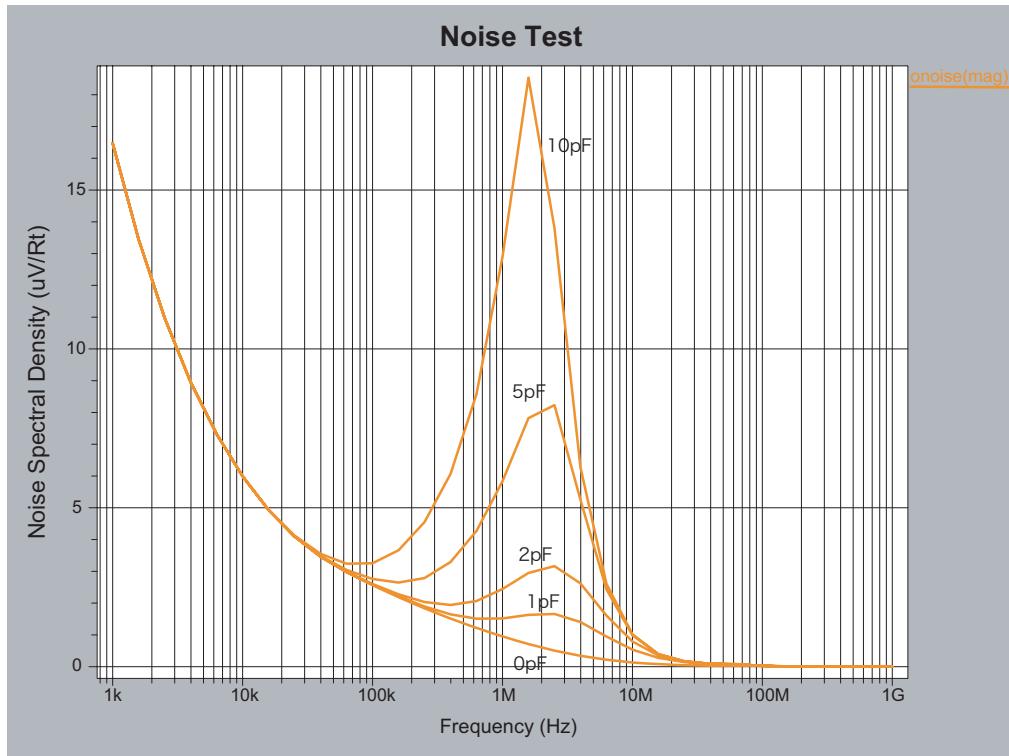

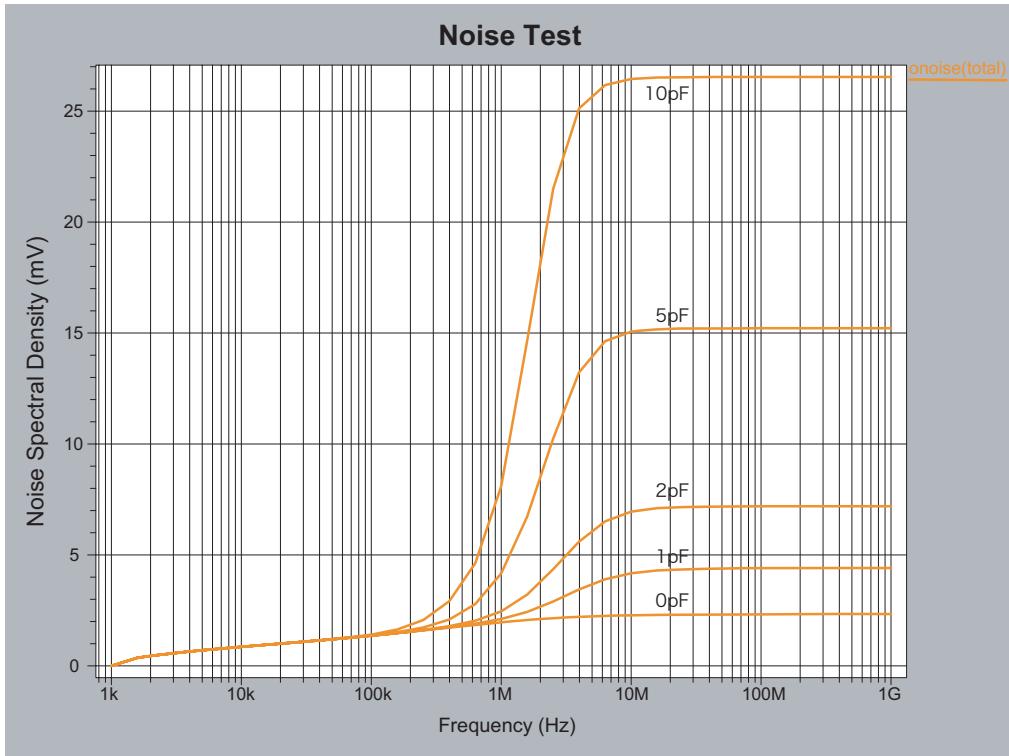

| 4.9 雑音スペクトル(周波数特性)                          | 72 |

| 4.10 雑音スペクトル(周波数領域での積分値)                    | 72 |

| 4.11 電源電圧のゆれに対する感度の評価用セットアップ                | 73 |

| 4.12 電源電圧のゆれに対する感度テスト                       | 74 |

| 4.13 Pair Monitor のバックグラウンド処理のためのシミュレーション結果 | 75 |

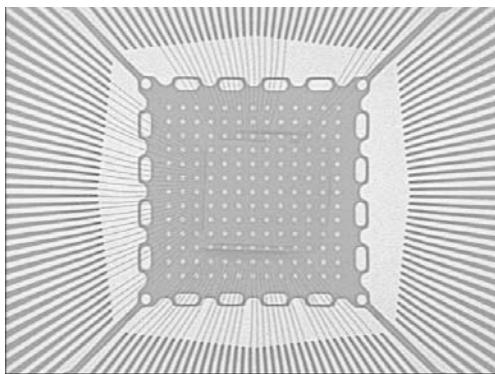

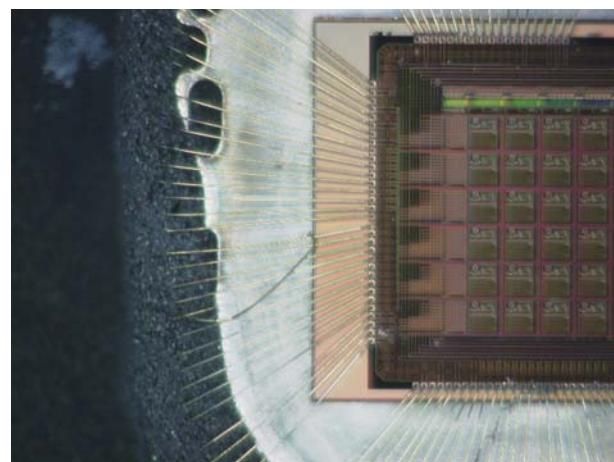

| <br>5.1 パッケージングされたチップ                       | 80 |

| 5.2 パッケージを開封したチップ                           | 80 |

|      |                                    |     |

|------|------------------------------------|-----|

| 6.1  | 評価試験フローチャート                        | 81  |

| 6.2  | チップ試験用の基盤                          | 82  |

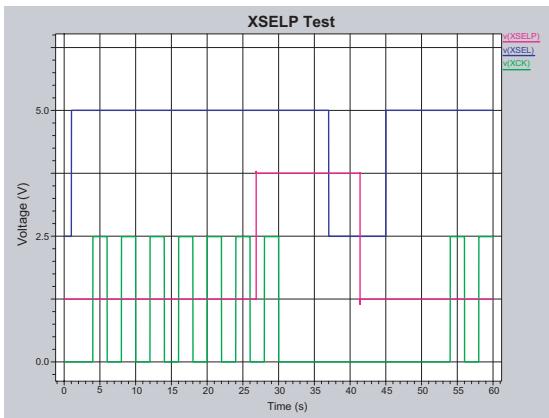

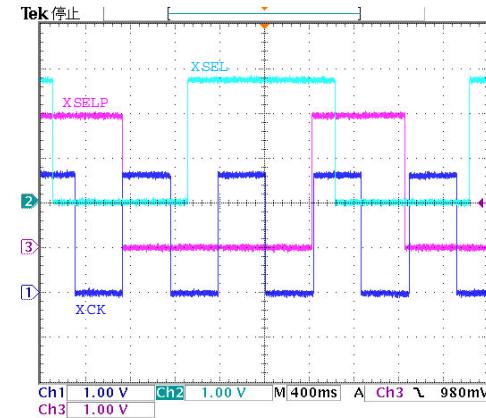

| 6.3  | シミュレーション結果                         | 84  |

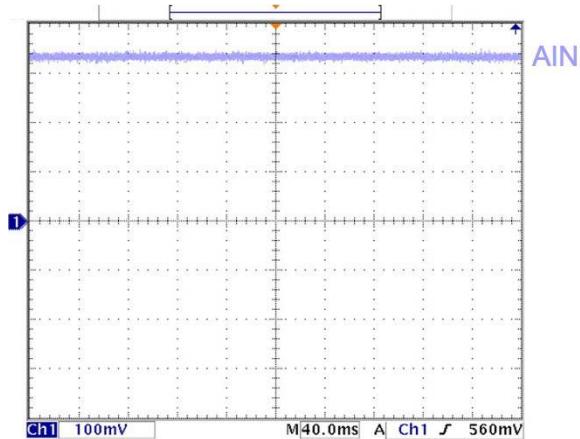

| 6.4  | オシロスコープ画面                          | 84  |

| 6.5  | バイアス回路内部におけるトランジスタの I-V 特性         | 85  |

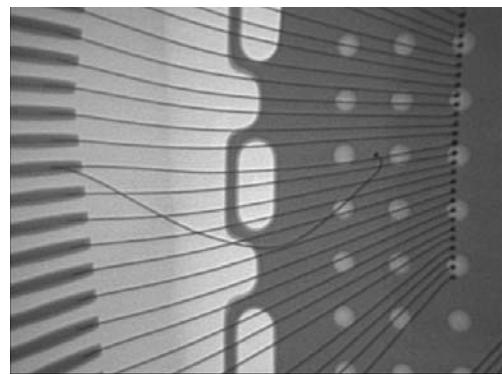

| 6.6  | チップ周辺図                             | 85  |

| 6.7  | 不良ワイヤリング                           | 85  |

| 6.8  | パッケージを開封したチップ                      | 86  |

| 6.9  | 不良ワイヤリング                           | 86  |

| 6.10 | AIN の測定結果                          | 87  |

| 6.11 | 液晶を塗布したチップ                         | 88  |

| 6.12 | 入力パッド付近の画像                         | 88  |

| 6.13 | 入力パッドのレイアウト図(左)と, その入力抵抗部を拡大した図(右) | 89  |

| 6.14 | FIB 加工前(左)と FIB 加工後(右)             | 89  |

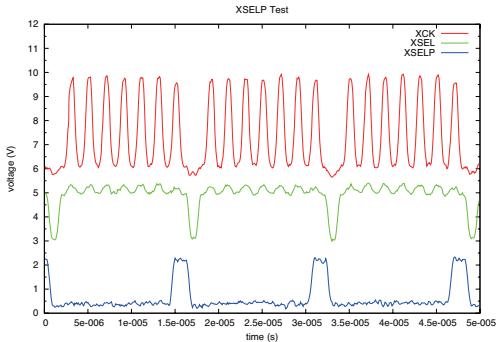

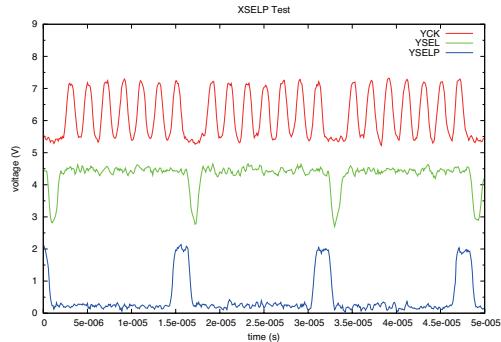

| 6.15 | XSELP の図                           | 90  |

| 6.16 | YSELP の図                           | 90  |

| 6.17 | 入力抵抗値を大きくした状態でのシミュレーション結果          | 90  |

| 6.18 | オシロスコープ画面                          | 90  |

| 7.1  | 発振現象                               | 93  |

| 7.2  | 修正後                                | 93  |

| B.1  | チップとピン配置の対応図                       | 95  |

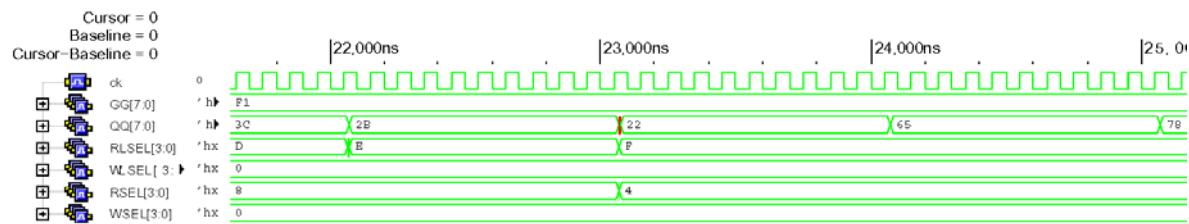

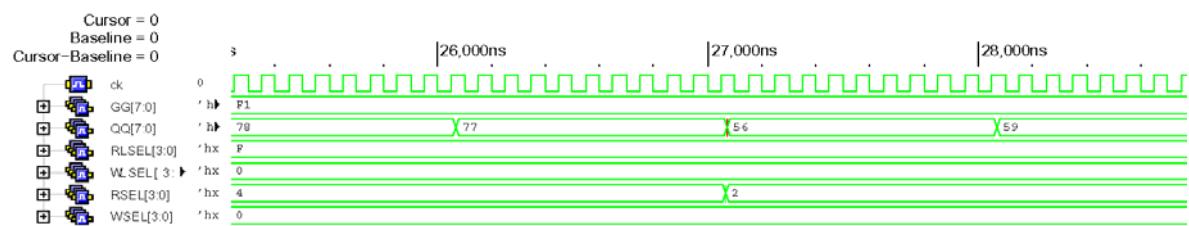

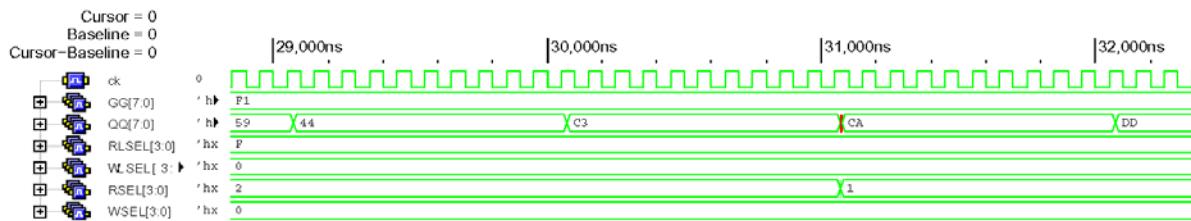

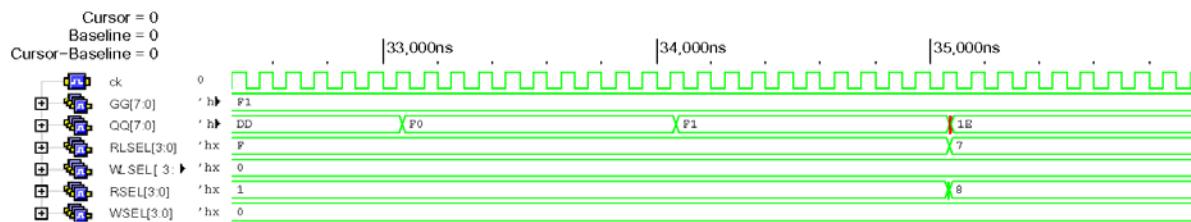

| C.1  | デジタル回路の波形(0ns ~ 7200ns)            | 100 |

| C.2  | デジタル回路の波形(7200ns ~ 21600ns)        | 101 |

| C.3  | デジタル回路の波形(21600ns ~ 36000ns)       | 102 |

# 表 目 次

|      |                                                     |    |

|------|-----------------------------------------------------|----|

| 3.1  | 常電導リニアコライダーと超伝導リニアコライダーのビームパラメータ                    | 31 |

| 3.2  | 前研究回路と本研究回路との比較                                     | 32 |

| 3.3  | 本研究回路の要求水準                                          | 33 |

| 3.4  | CHAIN1 回路の素子・端子の機能                                  | 37 |

| 3.5  | アナログ制御回路の素子・端子の機能                                   | 42 |

| 3.6  | DEC2 の真理値表                                          | 44 |

| 3.7  | モニタ回路の素子・端子の機能                                      | 45 |

| 3.8  | COUNT8 回路の素子・端子の機能                                  | 48 |

| 3.9  | 4 ビット数の 2 進コードとグレイコードの対応表                           | 49 |

| 3.10 | REGBNK4 回路の素子・端子の機能                                 | 49 |

| 3.11 | DEC2B 回路の素子・端子の機能                                   | 51 |

| 3.12 | DEC2B の真理値表                                         | 51 |

| 3.13 | DEC2N 回路の素子・端子の機能                                   | 52 |

| 3.14 | DEC2N の真理値表                                         | 52 |

| 3.15 | CAP0 回路の素子・端子の機能                                    | 54 |

| 3.16 | CAPB 回路の素子・端子の機能                                    | 55 |

| 3.17 | CAPXY                                               | 56 |

| 3.18 | CAPT 回路の素子・端子の機能                                    | 58 |

| 3.19 | CAPL 回路の素子・端子の機能                                    | 60 |

| 4.1  | アナログ部の評価用回路図の入力信号                                   | 64 |

| 4.2  | 電子雑音評価用回路図の入力信号                                     | 70 |

| 4.3  | 入力容量と電子雑音の関係                                        | 71 |

| 4.4  | 電源電圧の揺れに対する感度評価用回路図の入力信号                            | 73 |

| 4.5  | 本回路セットアップにおける入力信号                                   | 75 |

| 4.6  | デジタル回路のシミュレーション結果                                   | 77 |

| 5.1  | 試作チップの仕様                                            | 78 |

| 6.1  | 電源電圧の名称とその役割                                        | 83 |

| 6.2  | バイアス端子の名称とその役割                                      | 83 |

| B.1  | B1 ~ B32 ( 通番 1 ~ 32 ) のピンレイアウト                     | 96 |

| B.2  | R1 ~ R2 ( 通番 33 ~ 64 ) のピンレイアウト ( 本回路においては使用していない ) | 97 |

| B.3  | T1 ~ T32 ( 通番 65 ~ 96 ) のピンレイアウト                    | 98 |

|                                   |     |

|-----------------------------------|-----|

| B.4 L1～L32 ( 通番 97～128 ) のピンレイアウト | 99  |

| C.1 信号名の説明                        | 100 |

# 第1章 序論

素粒子物理学の発展は、原子、原子核、核子（陽子・中性子）、クォークと物質の内部構造を次々と明らかにし、粒子間の相互作用の究明により素粒子の統一的描像を与えてきた。これらは特に加速器技術の発展を背景として構築されてきたものである。現在ではクォークとレプトンからなるフェルミオンを基本粒子とし、グルーオン、光子、 $W$  及び  $Z$  といったゲージ粒子がそれらの相互作用の媒介をするという標準模型が、数多くの加速器実験によりによりその正当性を確認されている。一方で、この模型によれば質量が無いはずの  $W$  ボソンや  $Z$  ボソン、そしてクォークやレプトンといったフェルミオンの質量が測定されているという矛盾も生じている。この矛盾を解くためには「真空の自発的対称性の破れ」が必要であり、このメカニズムを解く鍵となるのが、未だに発見されていないヒッグス粒子である。このヒッグス粒子の発見、そして、TeV 領域で開くであろう標準模型を超える新たな物理へ挑戦するためにも、更なるエネルギー・フロンティアでの実験が必要不可欠である。

## 1.1 ILC 実験計画

International Linear Collider (ILC) 実験計画は、エネルギー・フロンティアの電子・陽電子衝突型加速器による実験計画である。そして、その計画は第一期、アップグレード期に分けることができる。第一期では  $500\text{GeV}$  の重心エネルギーを目標とし、続くアップグレード期では約  $1\text{TeV}$  の重心エネルギーを目標としている。このエネルギーは、ビッグバン直後  $10^{-12}$  秒、温度で  $10^{16}$  度に対応しており、 $10^{-18}\text{m}$  という微小な構造まで探索することができる（図 1.1）。一方で、現在 CERN で開発されている陽子・陽子衝突型加速器、LHC (Large Hadron Collider) の重心エネルギーは  $14\text{TeV}$  であり、単純にその重心エネルギーだけを比較するのであれば LHC の方が ILC よりもはるかに優れているかのように見える。しかし、LHC はそれ自体が構造を有する陽子・陽子の衝突型加速器であるために、その反応は非常に複雑であり、衝突エネルギーの一部分しか興味深い物理に関わらない。また、バックグラウンド事象が多いために素過程の厳密な測定は困難である。その点、養子のような内部構造を持たない電子・陽電子の衝突型加速器である ILC では、衝突エネルギーの全てを興味深い物理過程に使うことが可能である。また、その反応は素過程そのものであり、非常にクリーンな環境で精密な測定が可能である。

加速器の形状については、これまでの円形衝突型加速器ではシンクロトロン輻射によるビームエネルギーの損失が大きいため、実質的には LEP (Large Electron Collider) での重心系エネルギーが限界であると考えられている。この問題の解決のために線形衝突型加速器が提案された。加速方式については、日本を中心とし、アジアで開発されていた Global Linear Collider (GLC) までは常電導加速方式を採用していたが、2004

年8月の世界会議において世界中のリニアコライダー計画が一本化され，その名称はILCと名づけられ，その加速方式には超伝導が採用されることになった．

ILCにはそのエネルギー frontierでの精密な実験により，ヒッグス粒子の探索，まだ十分に研究の行われていない粒子であるトップクォークの精密測定，超対称性粒子の探索など，極めて多くの成果が期待されている．図1.2にILCにおいてターゲットとしている物理と，その重心エネルギーを示した．

図1.1: 初期の宇宙のエネルギーと温度．ILCの衝突エネルギーはビッグバン直後  $10^{-12}$  秒の温度に対応している [3] ．

図 1.2: ILC での物理のターゲットと重心エネルギー [3]

## 1.2 ILC が挑戦する物理

先に述べた通り，ILC は様々な物理現象の究明に挑戦していく．以下ではそれらの物理現象と ILC の果たす役割について，簡単に紹介していくこととする．

### 1.2.1 Higgs study

ヒッグス場は標準理論においてその存在を予言されており、そのポテンシャルに起因した自発的対称性の破れによって粒子の質量を生成するものと考えられている．例えば繰り込み可能な最低次のヒッグスポテンシャル

$$V(\phi^2) = -\mu^2 \phi^2 + \lambda \phi^4 \quad (1.2.1)$$

を仮定すると、このポテンシャルの最小値が  $\phi = 0$  から外れた点 ( $\equiv v/\sqrt{2}$ ) にあるために、低エネルギー領域では自発的対称性の破れが起こり粒子は質量を獲得する．この仮定におけるゲージボソンやフェルミオンの質量は  $m_W = \frac{1}{2}gv$ ,  $m_Z = \frac{1}{2}\sqrt{g+g'}v$ ,  $m_f = \frac{y_f}{\sqrt{2}}v$ ,  $m_H = \sqrt{\lambda}v$  となる．ここで  $v \sim 246\text{GeV}$  であり、 $g$ ,  $g'$  はそれぞれ  $SU(2)$ ,  $U(1)$  に対する結合定数、 $y_f$  はフェルミオン  $f$  に対する湯川結合定数であり、ヒッグスとの相互作用の強さがその粒子の質量を決定する形となる．このように標準理論においてヒッグス機構は粒子に質量を与える本質的な機構であり、ヒッグス粒子の発見とその研究は標準理論、さらにはそれを越える理論（超対称性理論など）にとって非常に重要な課題となっている．しかし、現在までの実験ではヒッグス粒子は発見されていない．ILC ではこのヒッグス粒子の発見が目的の一つであるが、多くのヒッグス粒子を

発見すること、そして発見された粒子の精密測定をすることがより大きな目的である。ヒッグス粒子の質量領域はモデルによって異なるが、いずれのモデルにせよ 250GeV 以下であると考えられている。この領域は初期の ILC 計画が問題なくカバーしている領域である。

図 1.3: ヒッグス粒子の探索に用いられる反応 [2]

ILC におけるヒッグス粒子の探索は図 1.3 のような反応を用いて行われる。(a) の Higgsstrahlung 反応は低エネルギーでのヒッグス粒子の生成に対する主要な反応であり、ILC の初期の段階において利用される。この反応は  $Z$  の崩壊モードによって (1)  $q\bar{q}$  ( $\sim 70\%$ )、(2)  $\nu\bar{\nu}$  ( $\sim 20\%$ )、(3)  $\tau^+\tau^-$  ( $\sim 3\%$ )、(4)  $e^+e^-$  or  $\mu^+\mu^-$  ( $\sim 6\%$ ) の 4 つのモードに分類することができる。また標準理論の枠組みにおけるヒッグス粒子の崩壊に関しては、ヒッグス粒子の質量が 140GeV 以下の時は  $b\bar{b}$  へ、140GeV 以上の時は  $W^*W$  への崩壊が主要な崩壊モードとなる。これらの崩壊モードに対して、2 ジェット、ニュートリノによる 4 元運動量欠損、あるいはレプトン対の不变質量に  $Z$  の不变質量 ( $= 91.2\text{GeV}$ ) を要求し、残りの 2 ジェットの不变質量を計算することによってヒッグスの探索は可能となる。またさらに (4) のモードはクリーンなモードであるため、ヒッグスの崩壊モードに無関係に（仮にヒッグスが測定不可能なモードに崩壊した場合でも）レプトン対を用いた質量欠損法によってヒッグスの質量の測定が可能となる。

我々の自然に対する理解が完全に間違っていない限り、ヒッグス粒子が ILC で観測されることは疑いようのないことである。仮に、ヒッグス粒子が ILC で観測されなかつたとしたら、それこそ新しい物理の扉を開く『偉大な発見』と言うこともできる。

### 1.2.2 Supersymmetry

超対称性理論 (SUSY) では、標準理論の枠組みに収まる粒子の全てに対して、スピンが  $1/2$  だけ異なる超対称性粒子が存在することを予言する。超対称性粒子のなかで一番質量の軽いものは安定な中性粒子であると考えられ、これを LSP と呼んでいる。LSP は暗黒物質の有力候補とも考えられている。少なくとも一つの超対称粒子の発見が、超対称性理論を保障するためには必要不可欠である。超対称性理論を探索する手段は、最初に見つかるのがどの超対称性粒子であるかはモデルに依存するが、モデルに依存しない方法である。一度、超対称性粒子が発見されれば、それは更なる発見への指針となる。しかし、実際には超対称性粒子の発見に関しては、LHC にその期待が寄せられており、LHC では不可能である粒子の精密測定をすることが、ILC のより重要な目的となる。具体的には超対称性粒子の質量やカップリングの精密測定、スピ

ンやハイパーチャージなどの量子数の測定，超対称理論が予言する結合定数の測定があげられる。

より大きな物理の発見のためには，LHC と ILC が相互に補完しあうことが重要である。LHC で得られた超対称性粒子の質量領域の情報は，ILC における  $e^+e^-$  ビームエネルギーを調整する指針となり，ILC において超対称性粒子の測定時におけるバックグラウンドを低減するのに非常に役立ち，精密な測定が可能となる。逆に，ILC での精密測定の結果が LHC の解析に役立つことにもなる。

具体的に ILC で行われる超対称性粒子の解析の一例として，スレプトン（スタウ以外）の解析を挙げておく。この解析では右巻きスレプトン ( $\tilde{l}_R^\pm$  :  $l \neq \tau$ ) がレプトン ( $l^\pm$ ) と LSP ( $\tilde{\chi}_1^0$ ) へ崩壊するモードである

$$e^+e^- \rightarrow \tilde{l}_R^+\tilde{l}_R^- \rightarrow l^+\tilde{\chi}_1^0 l^-\tilde{\chi}_1^0 \quad (1.2.2)$$

が用いられる。ここで，このモードの解析ではニュートリノを含むような標準理論のプロセス ( $e^+e^- \rightarrow WW$ ,  $W \rightarrow l\bar{\nu}$ ) がバックグラウンドとなるが，そのようなバックグラウンドは加速電子を偏極させることによって押さえられる。

### 1.2.3 Top Quark Study

トップクォークはこれまでに発見された素粒子の中で最も重い粒子であり，CDF と D0 の結果によれば [4]

$$m_t = 174.3 \pm 3.2(stat.) \pm 4.0(syst.) \text{ GeV/c}^2 \quad (1.2.3)$$

である。これは標準理論のラグランジアンにおけるトップクォークの質量項が  $SU(2)_L \times U(1)_Y$  対称性を最も大きく破っていることを意味する。そして，トップクォークの精密測定はフレーバー構造の起源を理解する上で重要になってくる。実際には，トップクォークのスレッシュヨールド領域 ( $\sqrt{s} \approx 2m_t$ ) における  $e^+e^- \rightarrow t\bar{t}$  の崩壊モードを用いて，トップクォークの質量や崩壊幅の精密測定が行われる。この崩壊モードにおけるトップクォークは編極しており，トップクォークの性質を調べるための理想的な環境となっている。

標準理論ではトップクォークは，ほぼ 100% で  $b, W$  へ崩壊すると考えられており，崩壊幅は理論的な予測から上記の質量幅においては 1.5 GeV 程度と考えられている。ILC では精密に崩壊幅を測定でき，理論的予測からのずれが観測されれば，それは，第 4 世代の存在，あるいは  $t \rightarrow bH^+$ ,  $t \rightarrow \tilde{t}\tilde{\chi}$  といった崩壊モードを示唆するものであります。

### 1.3 ILC の構成

図 1.4: ILC の概念図 [14]

図 1.4 に現在の ILC デザインの概念図を示す。各部分の役割を以下に記述する。

- 電子源

電子ビームを発生させる部分である。この部分は非常に小さいため、図には描かれていません。図左側の 5-GeV Linac の先端にあり、直後に電子は 5GeV まで加速される。ILC では編極電子源を標準にしている。

- 減衰リング (DR)

5GeV まで加速した電子・陽電子を 200ms 蓄積し、規格化工ミッタンスの小さなビームにする。陽電子側は、2 段重ねのリングになっている。

- RTML (Ring To Main Linac)

減衰リングを出てから、ビームは一旦衝突点とは逆向きに走り、180 度の旋回軌道の後、主線形加速器に入る。この間を RTML と呼んでいます。旋回軌道の終端付近の Spin Rotator (SR) で衝突点でのスピンの向きを調整する。その後の bunch compressor (BC) で減衰リングでのバンチ長 (数 mm) を数  $100\mu\text{m}$  に圧縮する。

- 主線形加速器 (Main Linac)

電子・陽電子を実験に必要なエネルギーまで加速するもので、リニアコライダー全施設の中で、最大かつ最も高価なものである。ILC 第 1 期 (重心エネルギー 500GeV) では電子・陽電子側それぞれ約 11km である。

- Undulator

陽電子を発生させる方法である。電子ビームが 150GeV まで加速されたところにこの装置を置いて、陽電子を作り、長い輸送ラインで反対側に運ぶ。

- BDS (Beam Delivery System)

加速終了から衝突点までの装置の総称である。衝突点でのビームサイズを小さくするためのレンズ (磁石) 系が主なもので、電子側と陽電子側の合計で全長 5.5km の巨大なものである。

- IP (Interaction Point)

2 つのビームの衝突点で、実験のための検出器が置かれる。ビームは完全な正面衝突ではなく、14mrad の小さな交差角をもって衝突する。

## 1.4 ILC 検出器の概要

図 1.5: GLD 検出器の外観 [3]

電子、陽電子衝突実験である ILC では、LHC のようなハドロンコライダーに比べて、全重心系エネルギーが反応の素過程に使用されるため、終状態の識別が容易であり確実な新粒子探索や精密実験が可能である。ILC と LHC との関係について、LHC 実験は「新粒子発見の実験」であり、ILC 実験は「物質と力の構造を解明し確定する実験」と言えるであろう。そのため ILC では、その利点を最大限に引き出すような、精度の良い解析を行うことのできる測定器が要求され、その検出器の満足すべき性能としては以下のような事が挙げられている。

- $W$  と  $Z$  ボソンについて、それらの主要な崩壊モードである  $q\bar{q}$  の 2 ジェットイベントにおける質量分解能が、その崩壊幅 (2.5GeV と 2.0GeV) と同程度であること。つまりはそれらが分別可能であること。

- $b, c$  及び (可能ならば)  $s$  クォークの識別が高精度で可能であること。

- $e^+e^- \rightarrow ZH$  ( $Z \rightarrow \ell\bar{\ell}$ ) イベントに対する、質量欠損法によって得られるヒッグス粒子の質量分解能について、飛跡検出器の運動量分解能から来る影響が、ビームエネルギーの広がりからくる影響よりも十分小さいこと。また SUSY カスケードについてもレプトンの運動量計測が可能であるような、運動量計測可能域を実現すること。

- 測定可能角度領域を、ビームパイプとバックグラウンド対策用のマスキングシステムが設置される前後方領域を除く領域とする。高エネルギーになるほど 3 対以上の終状態の過程が増すため、十分広い立体角を隙間無く覆うことが重要である。これはまた、ニュートリノのような直接検出不能な粒子の運動量の間接測定の可能性を保障することにもなる。

- 各イベントの区別のため、各ビームバンチにおけるイベントを可能な限り区別できるような時間分解能を持つこと。

アジアでは以上の条件を満たす検出器デザインとして GLD 検出器の研究開発が進められている。本研究もこの GLD 検出器に基づいた研究である。GLD 検出器は崩壊点検出器 (VTX)、中間飛跡検出器 (SIT)、タイムプロジェクションチェンバー (TPC)、カロリメータ (CAL)、 $\mu$  粒子検出器などから構成されている。図 1.5 に GLD 検出器の外観を、図 1.6 に GLD 検出器を構成する各検出器の位置関係を示した。以下において、それら各検出器について記述する。

図 1.6: 各検出器の位置関係

#### 1.4.1 崩壊点検出器 (VTX)

図 1.7: 崩壊点検出器の構造図 [1]

崩壊点検出器は検出器群の中で最内層に位置し、荷電粒子の飛跡を精密測定する測定器である。この検出器は  $B$  中間子や  $D$  中間子の崩壊点を測定し、 $b$  クォークや  $c$  クォークを同定する役割を担っている。この崩壊点検出器で  $b$ ,  $c$  クォークのジェットの識別を精度良く行い、 $u$ ,  $d$ ,  $s$  のような軽いクォークを効率よく排除するために、非常に高い飛跡再構成能力が要求される。このために、検出器自体の位置分解能が高いことは勿論、検出器が可能な限りビーム衝突点の近くに設置される必要がある。その

ため，衝突点において  $W$  対生成， $Z$  対生成により発生した多数の粒子やバックグラウンド X 線などにさらされる。従って，崩壊点検出器には強い放射線耐性を持ち，これらのバックグラウンドによる飛跡と目的とする粒子による飛跡を区別できる高い分解能が要求される。

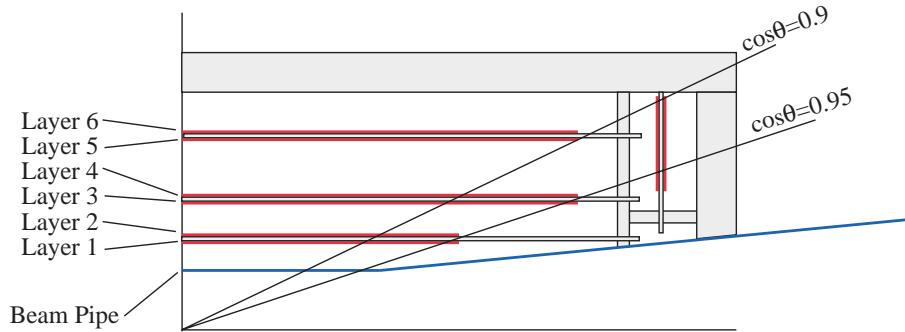

現段階ではファイン・ピクセル CCD の技術を用いた崩壊点検出器の開発が進められている。その検出器の構造図を図 1.7 に示した。検出器はビーム軸に巻きつくようなバレル状をした 3 枚のプレート，6 層の CCD ウェーハー，及び前方に取り付けられたビーム軸に垂直な面上に配置される 1 枚のプレート，2 層の CCD ウェーハーからなる。それぞれのプレートの厚さは 2mm であり，それを挟み込むように厚さ  $50\mu\text{m}$  以下の 2 枚の CCD ウェーハーが取り付けられる。 $\cos\theta < 0.9$  の領域を 6 層の CCD ウェーハーで覆っており， $\cos\theta < 0.95$  の領域を 4 層の CCD ウェーハーで覆っている。

#### 1.4.2 中間飛跡検出器 (SIT)

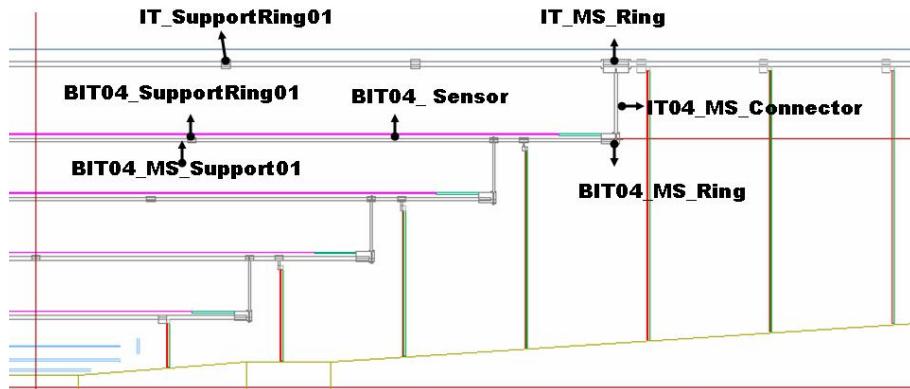

中間飛跡検出器は，崩壊点検出器と TPC によるトラッキングを補完して運動量分解能を向上させるために，崩壊点検出器と TPC の間の領域に設置される。中間飛跡検出器はビーム軸に巻きつくようなバレル状の Barrel IT (BIT) 4 層と，ビーム軸に垂直な面上に配置される Forward IT (FIT) 7 層によって形成される(図 1.8)。BIT は各層の両面に  $z$  及び  $r - \phi$  方向に沿った Si ストリップ型検出器 (DSSD) を持つような構造になっており，DSSD はストリップピッチが  $50\mu\text{m}$  である  $511$  の  $n^+$  ストリップと，ストリップピッチが  $100\mu\text{m}$  である  $511$  の  $p^+$  ストリップから構成される。FIT は内側の 3 層がピクセル検出器から構成され，外側の 4 層がストリップ型検出器から構成される。要求される位置分解能は BIT では  $10\mu\text{m}$  であり，FIT では  $25\mu\text{m}$  である。

図 1.8: 中間飛跡検出器の構造図 [1]

#### 1.4.3 タイムプロジェクションチェンバー (TPC)

タイムプロジェクションチェンバー (TPC) は，端部にマイクロパターン検出器 (MPDG) が 2 次元的に敷き詰められていて，空間にはガスが充満し，MPDG に垂直な高電磁場がかかっている。TPC 中を荷電粒子が通ると，荷電粒子の通過によって作られた電離電子は電場によって，MPDG の方向にドリフトする。MPDG に到着した

電子は強い電場で電子雪崩を起こし、数千倍に増幅される。電子のドリフトにかかる時間情報とMPDGによる2次元の空間情報とによって荷電粒子の飛跡が再構成される。ここで電場と平行にかけられた磁場によって電離電子の拡散が抑制され、分解能の向上に役立っている。また、TPCによって測定された  $dE/dx$  は様々な物理解析に用いられ、運動量の情報と合わせて  $\pi^{pm}$ ,  $K^{pm}$ ,  $p$ ,  $e^{pm}$  などの区別にも利用される。TPCに要求される性能はトラッキング効率が98%以上のトラッキング効率、 $5 \times 10^{-5} / \text{GeV}/c$  程度の運動量分解能、4.5%以下の  $dE/dx$  分解能などが挙げられる。

#### 1.4.4 カロリメータ

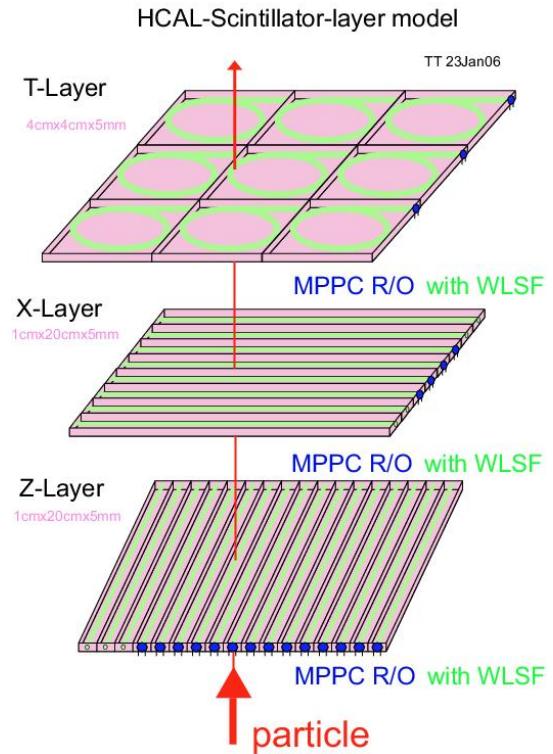

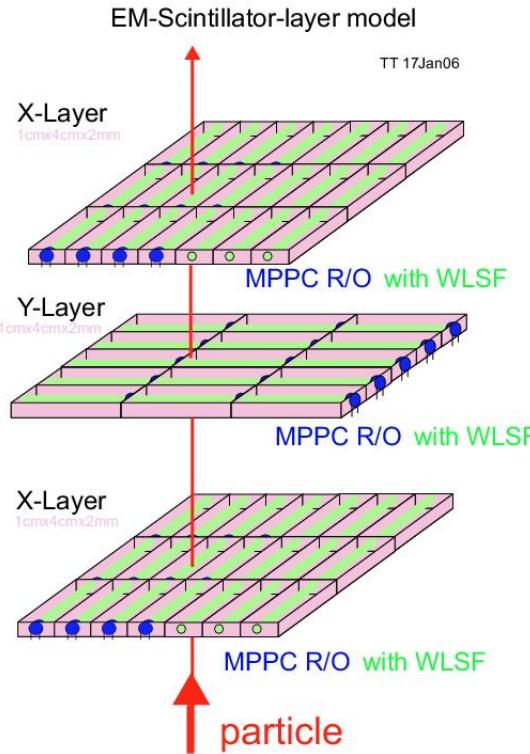

図 1.9: 電磁力カロリメータの構造図 [1] 図 1.10: ハドロンカロリメータの構造図 [1]

飛跡検出器が荷電粒子に対してのエネルギーや運動量を測定する役割を担っているのに対して、カロリメータの役割は中性粒子のエネルギーと運動量の測定である。具体的には、各粒子によるシグナルを分離できること、再構成されたカロリメータの各クラスター（粒子ごとのヒット群）に対して、もとのエネルギーを精度良く再現できることなどが要求される。

そのためカロリメータでは  $\mu$  粒子などを除く生成粒子がカロリメータの中でシャワーを起こして、そのエネルギーのほとんど全てをカロリメータ内で落とすに十分な吸収層を設置し、そのエネルギー・デポジットの一部を測定することによって、粒子のエネルギーを推測できるように設計されている。具体的には物質量の大きい物質で構成された吸収層と、シグナル測定のための測定層を交互に配置している。

また、カロリメータでは光子と中性ハドロンとの物質中での反応の違いを考慮し

て，内側に電磁力カロリメータ (ECAL) を設置し，その外側にハドロンカロリメータ (HCAL) を設置する設計になっている。図 1.9, 図 1.10 に電磁力カロリメータ，ハドロンカロリメータの構造図をそれぞれ示した。ECAL の各層は厚さ 3mm のタンゲステンからなる吸収層と，厚さが 2mm で平面サイズが  $1cm \times 4cm$  のストリップ構造をしたシンチレータからなる測定層により構成される。一方，HCAL の各層は厚さ 5mm の鉛からなる吸収層と，厚さが 5mm で平面サイズが  $1cm \times 20cm$  のストリップ構造をしたシンチレータからなる測定層により構成される。

#### 1.4.5 $\mu$ 粒子検出器

$\mu$  粒子検出器では  $\mu$  粒子の同定を行う。GLD の一番外側に位置し，鉄と棒状のシンチレータの積層構造からなる。 $\mu$  粒子は多くの場合，新粒子探索における重要な信号となるため，立体角をできるだけ広く覆うとともに隙間のないように配置される必要がある。 $\mu$  粒子はその性質からカロリメータを突き抜けて，その外側まで到達することが多く，カロリメータの外側にある  $\mu$  粒子検出器のシグナルと，飛跡検出器から得られたトラックをつなげることにより  $\mu$  粒子の同定を行う。飛跡検出器によって再構成されたトラックとの連結が可能な分解能が要求される。

### 1.5 ビームプロファイル

未知の高エネルギー粒子の探索には，高品質（低エミッタンス），大電流，超高エネルギーの電子・陽電子ビームの生成が要求される。物理実験及び加速器運転時に，このような高品質なビームの生成，輸送，加速，維持をいかに行うかが重要である。そのためには，ビームの状態（サイズ，位置，エネルギーなど）を把握する必要があり，ビームプロファイルモニタが重要な役割を果たす。しかし，衝突点付近においては，ビームサイズをナノメータレベル ( $\sigma_x/\sigma_y = 655nm/5.7nm$ ) まで絞りこむため，その測定は極めて困難である。ナノメータサイズのビームを測定する方法としてレーザーの干渉を利用する方法がある[7]。これは，電子ビームの軌道をレーザー干渉縞の横切る方向にスキャンし，レーザーとビームの衝突時に生じるコンプトン散乱光の強度分布を測定することによりビームサイズを測る。既に，この方法により SLAC の FFTB (Final Focus Test Beam) で  $\lambda = 1.064\mu m$  の Nd:YAG レーザーを用いて  $60nm$  のビームサイズを測定することに成功している。しかし，粒子検出器の障害にならないようにレーザー干渉モニタを作ることは困難であること，また，この方式により測定できるビームサイズの限界は  $5nm$  程度であることから IP 付近でのビームプロファイルモニタには適さない。そこで，田内氏と横谷氏によって考案されたのがビーム-ビーム相互作用によって発生する  $e^+e^-$  ペアを利用する方法であり，その原理を用いたビームプロファイルモニタとして Pair Monitor の研究開発が進められている[5]。Pair Monitor は衝突点から  $400cm$  の位置に設置される。Pair Monitor の後方には最終収束四極磁石 (QC1) が設置されるが，QC1 からの反跳電子を効果的に吸収するためにカーボンマスクが Pair Monitor と QC1 との間に設置される。Pair Monitor の詳細については 2 章で述べる。

## 第2章 Pair Monitor

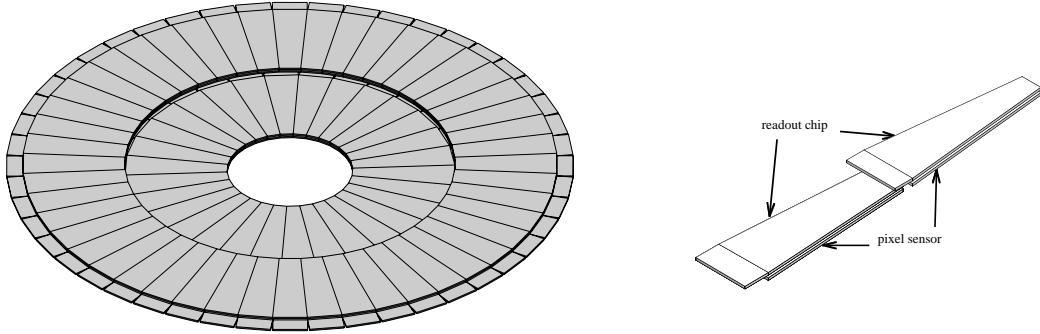

図 2.1: Pair Monitor (左) とその構成要素 (右) [16]

Pair Monitor は 35000 の 3D シリコンピクセルセンサーと , それぞれのピクセルセンサーにバンプボンドされた  $400\mu\text{m} \times 400\mu\text{m}$  の読み出し回路から構成され , その内径は  $2\text{cm}$  , 外径は  $8.5\text{cm}$  である . 加速管内の電場はビームトレンイン内のバンチが作る電場によって影響を受け , その電場はそれ以降のバンチに影響を与えビームは不安定になってしまふ . それを避けるために , トレンイン内のバンチ情報をモニターし , その情報をもとに加速器の運転に実時間でフィードバックすることで , 安定したビーム供給に資することが Pair Monitor の目的である . 衝突点において対生成した  $e^+e^-$  ペアは同電荷を持つビームによって散乱され , Pair Monitor に衝突する . その  $e^+e^-$  ペアの Pair Monitor 上の分布を解析することでビームの情報を得ることができる .

以下の節では Pair Monitor の原理 , 3D シリコンピクセルセンサー , 読み出し回路について述べている .

### 2.1 Pair Monitor の原理

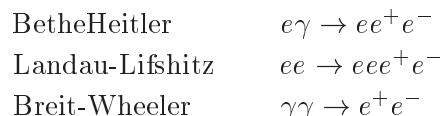

Pair Monitor におけるビームプロファイルの方法はビーム-ビーム相互作用により発生する  $e^+e^-$  ペアを利用し , ビームサイズ ( $\sigma_x \sigma_y$ ) を測定するものである .  $e^+e^-$  ペアは , 以下の 3 つの非コヒーレントな過程によりほとんどビーム軸にそって生成され , そのエネルギーは非常に低エネルギーにピークを持つ .

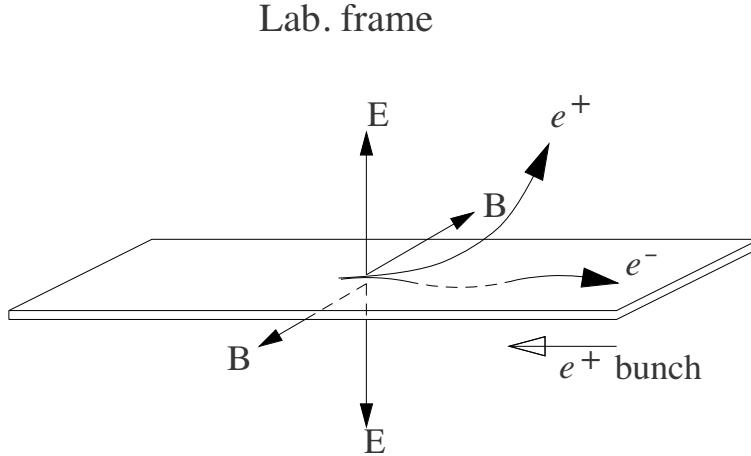

そして、この  $e^+e^-$  ペアはビームの作る電磁場により力を受け曲げられる。バンチは非常にフラットであり ( $\sigma_y \ll \sigma_x$ )、向かってくるビームの電荷と生成された粒子の符号が同じであれば縦方向に大きく散乱される。それに対し、粒子の電荷の符号が反対であればビーム面を振動し、大きく散乱されることはない。この過程を図 2.3 に示した。

図 2.2: ビームの電磁場による  $e^+e^-$  の散乱 [6]

この大きく散乱された粒子の散乱角分布はビームの形（電場の形）に依存するため、ビームサイズの重要な情報を持つ。以下では、非コヒーレント過程により対生成した  $e^+e^-$  ペアが電磁場から受ける力、Pair Monitor 上での  $e^+e^-$  ペアの分布、 $\sigma_x$  の導出方法、及び  $\sigma_y$  の導出方法についてそれぞれ記述する。

なお、図 2.5、図 2.6、図 2.7、図 2.8、図 2.9 は GLC のビームパラメータを用いたシミュレーションによる図である。ILC と GLC ではビームパラメータが異なるが、同じ原理でビームプロファイルを測定できる。

### 2.1.1 $e^+e^-$ ペアが電磁場から受ける力の導出

$e^+e^-$  ペアが受けるクーロン力は、ほぼ光速度でのビーム衝突のためローレンツ収縮により、非常によい近似で 2 次元力となる。ビームの進行方向 ( $z$ ) に対して垂直な電場成分を考える。ビーム静止系での垂直方向の電場を  $E'_\perp$  とすると、重心系（実験室系）で観測される電場  $E_\perp$  と磁場  $B_\perp$  は、ローレンツ変換により

$$E_\perp = \gamma E'_\perp, \quad B_\perp = -\gamma v E'_\perp \quad (2.1.1)$$

となる。ここで  $v$  はビームの静止系に対する重心系の速度とする。この電磁場により電荷  $e$  速度  $v_e$  の粒子の受ける力  $F$  は

$$F = e(E_\perp + v_e \times B_\perp) \quad (2.1.2)$$

となる。ここで  $v = (0, 0, v)$   $v_e = (0, 0, \pm v_e)$  (符号は電荷の進む方向を示す) とする

と式 (2.1.1) より式 (2.1.2) の磁場による寄与は、

$$\mathbf{v}_e \times \mathbf{B}_\perp = \mathbf{v}_e \times \left( -\mathbf{v} \times \frac{\mathbf{E}_\perp}{c^2} \right) \quad (2.1.3)$$

$$= \pm \frac{1}{c^2} (vv_e E_x, vv_e E_y, 0) \quad (2.1.4)$$

$$= \pm \frac{vv_e}{c^2} \mathbf{E}_\perp \quad (2.1.5)$$

となる。つまり、

$$\mathbf{F} = e \left( 1 \pm \frac{vv_e}{c^2} \right) \mathbf{E}_\perp \quad (2.1.6)$$

となる。 $v \simeq v_e \simeq c$  なので、式 (2.1.6) よりビームと同じ方向に進む電荷の受ける力

はゼロとなり、反対方向に進む電荷は電場  $\mathbf{E}_\perp$  の 2 倍の力を受ける。つまり、対生成

された  $e^+e^-$  ペアは向かってくるビームによって散乱されるため、そのビームの情報

だけを持ち、同じ方向に進むビームの情報は持たない。

### 2.1.2 Pair Monitor 上での $e^+e^-$ ペアの分布

図 2.3: ビームの座標系 [16]

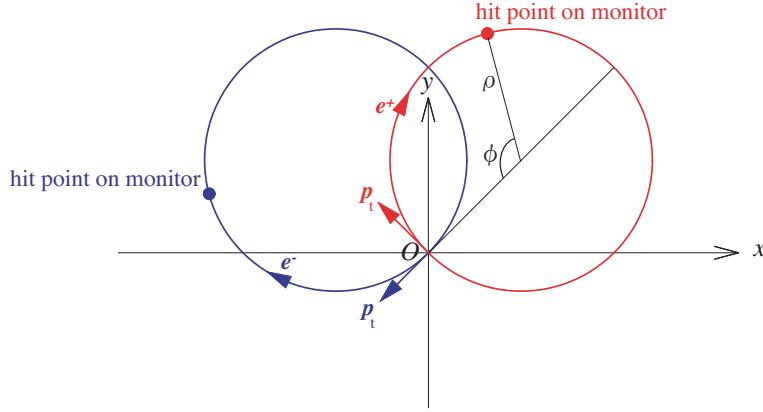

散乱された  $e^+e^-$  ペアは、検出器のソレノイド磁場によってビームパイプに巻き付

くように進み、衝突点から 400cm の位置にある Pair Monitor に衝突する。回転され

ることによりビームの情報が失われることはない。よって、Pair Monitor で粒子の衝

突した位置を測定し、その衝突位置の分布からビームサイズの情報を得ることができる。 $e^+e^-$  の衝突位置は  $B$ [Tesla] を検出器のソレノイド磁場、 $L$ [cm] を衝突点から Pair

Monitor までの距離、ビーム方向の運動量を  $p_z$ 、 $p_z$  に垂直方向の運動量を  $p_t$ [MeV] と

すれば、螺旋運動をする粒子の起動半径が  $\rho$ [cm] =  $p_t/3B$  となるので、

$$r = 2\rho \sin \frac{\phi}{2}, \quad \phi = \frac{3BL}{p_z} \quad (2.1.7)$$

と表すことができる。図 2.4 にそれらの位置関係を示した。

図 2.4: Pair Monitor 上での衝突位置

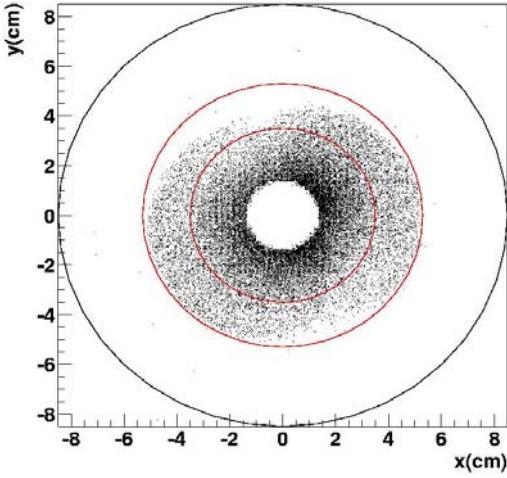

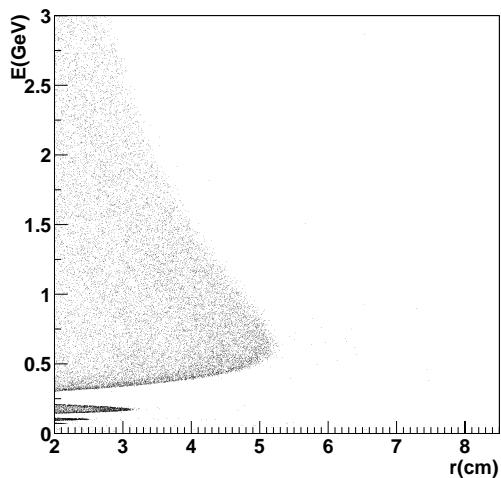

図 2.5 に陽電子ビーム側の Pair Monitor での衝突の分布を示す。図中の一番外側(半径 8.5cm)と内側(2cm)の円は Pair Monitor の縁を表す。陽電子ビーム側では、大きく散乱されるのは陽電子なので、この図の分布の大部分が陽電子によるものであり、ほとんど散乱されない電子は半径 2cm の円の内側を通るため Pair Monitor にはほとんど衝突しない。また、図から明らかなように半径 3~5 cm 辺りの分布が非対称になっている。これは衝突点で生成された  $e^+e^-$  ペアがソレノイド磁場によって螺旋運動しても、その散乱方向の非対称性が失われていないことを意味し、仮にビームが円形( $\sigma_x = \sigma_y$ )であれば、Pair Monitor 上の衝突分布に図 2.5 のような非対称性は現れない。つまり、この非対称性はビームサイズの情報を持つことを意味する。また、図 2.6 は Pair Monitor に衝突した粒子の半径位置とそのエネルギーの分布を示したものである。この図より明らかな最大半径をもつことがわかる。この最大半径  $r_{max}$  は上式より  $\phi = \pi$  のときであり  $p_t^{max} = p \sin \theta_{max}$ ,  $p_z \simeq p$  とすると、

$$r_{max} = 2\rho = \frac{2p_t^{max}}{3B} \simeq \frac{2L \sin \theta_{max}}{\pi} \quad (2.1.8)$$

となるため、 $r_{max}$  は  $\theta_{max}$  によって決まる。 $\theta_{max}$  はビーム-ビーム相互作用での散乱によって与えられるとして近似的に

$$\theta_{max} \simeq \left( \frac{\ln(\frac{4\sqrt{3}D_x}{\epsilon})}{\sqrt{3}\epsilon D_x} \right)^{1/2} \theta_0 \sqrt{2} \quad (2.1.9)$$

となる。ただし、これは  $D_x/\epsilon \geq 1$  であるときの近似解であり、 $\epsilon \equiv p/E_{beam}$ ,  $D_x \equiv 2Nr_e/\gamma \cdot \sigma_z/(\sigma_x(\sigma_x + \sigma_y))$ ,  $\theta \equiv D_x\sigma_x/\sigma z$  である。

図 2.5: 衝突位置の分布 [16]

図 2.6: 衝突位置半径に対するエネルギーの分布 [16]

### 2.1.3 $\sigma_x$ の導出

式 (2.1.9) において  $\sigma_x \ll \sigma_y$  として近似すると,  $\theta_{max}$  つまり  $r_{max}$  は  $\sigma_y$  に依らず,  $\sigma_x$  と  $N$  の関数となることが分かる. ここで, 1 バンチ当たりの粒子数  $N$  は壁電流モニターなどを用いることにより精度良く求めることができる. つまり Pair Monitor により  $r_{max}$  を測定することで  $\sigma_x$  を見積もることができる.

### 2.1.4 $\sigma_y$ の導出

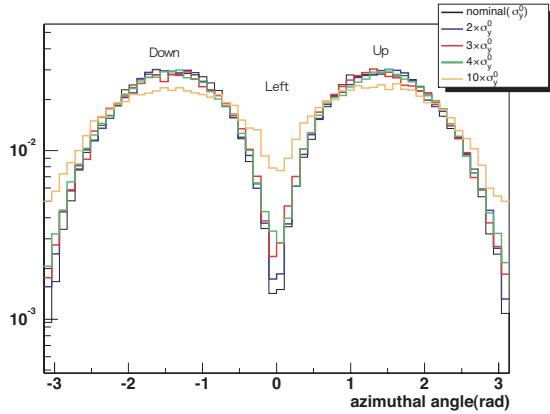

$\sigma_y$  を変化させたときの衝突点での散乱角分布及び Pair Monitor 上の方位角分布を図 2.7, 図 2.8 に示す. 図 2.7 より  $\sigma_y$  が変化することによって分布の山の谷の比が変化していることが分かる.  $\sigma_y$  が小さいと水平方向に散乱されにくくなり, 垂直方向により多く散乱されるということである. 分布が Left 領域に少し偏極しているのは, ビームの交差角が存在する衝突のためである. 次に, 図 2.8 を図 2.7 と比較すると, この領域での  $\phi_{PM}$  分布は,  $\phi_{ip}$  分布と線形依存していることが分かる. これはちょうどこの領域に衝突した粒子のソレノイド磁場による回転角が 360 度以下のものだけであるためで, これより内側の領域では 360 度以上回転したものと重なりあった分布となるため線形性は失われる. 又, Left と Right あたりの分布の違いは,  $\phi_{ip}$  分布でも見られたビームの交差角の存在によるものである.

図 2.7: IP での散乱角分布 [16]

図 2.8: Pair Monitor 上の方位角分布 [16]

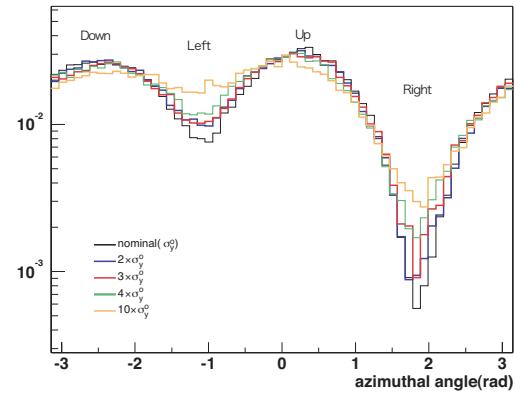

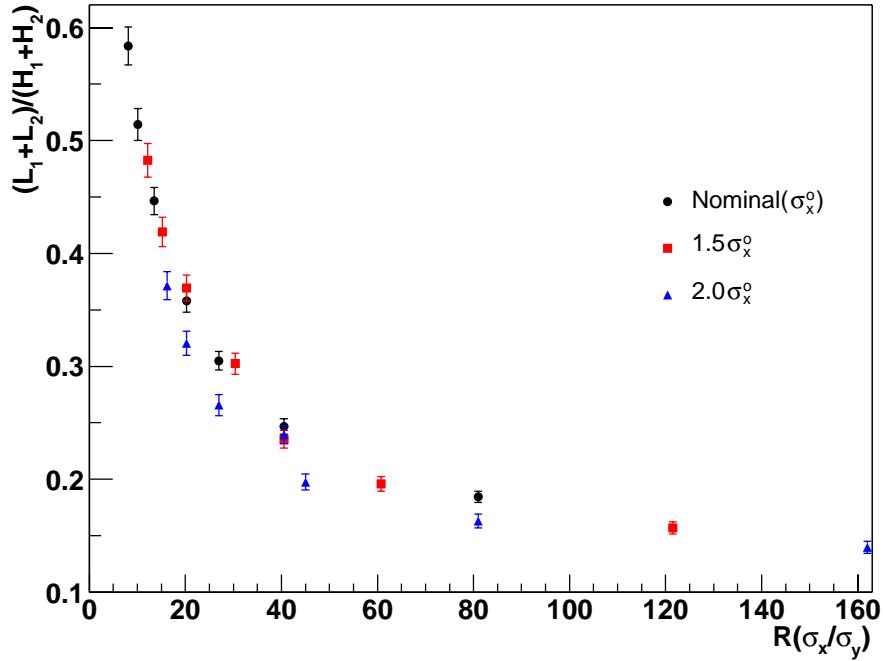

Pair Monitor の衝突分布の変化から垂直方向のビームサイズ  $\sigma_y$  の情報を抜き出すためには、図 2.8 から分かるように UP, Down, に対する Left, Right の比をとればよい。したがって Peak-to-valle ratio ( $R_{pv}$ ) を

$$R_{pv} \equiv \frac{L_1 + L_2}{H_1 + H_2} \quad (2.1.10)$$

と定義する。ここで  $L_1, L_2, H_1, H_2$  はそれぞれの領域に衝突した粒子数とする。この  $R_{pv}$  をアスペクト比  $R(\sigma_y/\sigma_x)$  に対してプロットすると、図 2.9 に見られるように  $R_{pv}$  は  $\sigma_x$  にはほとんど依存せず、アスペクト比の関数となっていることが分かる。既に見てきたように  $r_{max}$  より  $\sigma_x$  が求められるので、 $\sigma_y$  を見積もることができる。

図 2.9: アスペクト比に対し  $R$  に対する  $R_{pv}$  [16]

## 2.2 3Dシリコンピクセルセンサー

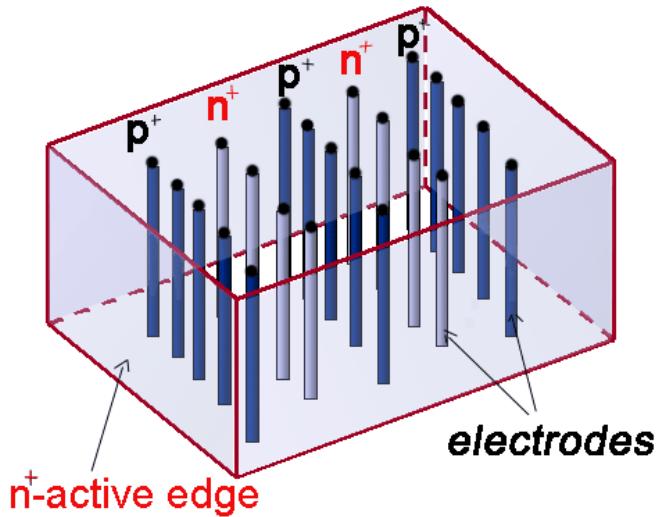

図 2.10: 3D ピクセルセンサー [9]

通常のピクセルセンサーはセンサーの上面と下面の電極に電圧をかけ空乏化させるが，S.Parker 氏によって考案された 3D シリコンピクセルセンサー [8] は図 2.10 にみられるように電荷を収集するポール状電極がシリコンを垂直に貫いている。このため，ガードリングを設ける必要がなくセンサーの縁も有効領域であり，このためデッドエリアが極めて小さい検出器を作ることが可能である。Pair Monitor に用いられる 3D シリコンピクセルセンサーは厚さが  $200\mu\text{m}$ ，平面のサイズが  $1\text{cm} \times 3\text{cm}$  程度を想定している。ピクセルセンサー上にはピクセルサイズが  $400\mu\text{m} \times 400\mu\text{m}$  の読み出し回路がバンプボンドされている。全空乏化電圧は  $10\text{V}$  以下であり，放射線を受けた後も空乏化電圧が大きく上昇することはない。

図 2.11 は  $e^+e^-$  ペアビームを Pair Monitor に入射し各ピクセルでのエネルギーデポジットを調べたものである。各ピクセルごと，粒子のトラックごと，及び，二次的な光子による各ピクセルごとのエネルギーデポジットをプロットしている。このシミュレーションのセットアップでは 20 バンチ相当の  $e^+e^-$  ペアビームをソレノイド磁場  $3\text{T}$  で螺旋運動させ，IP から  $176\text{cm}$  にある Pair Monitor に入射させている。また，Pair Monitor は内径  $2\text{cm}$ ，外径  $8.5\text{cm}$ ，厚さ  $300\mu\text{m}$  のシリコンディスクとし，読み出し回路のピクセルサイズを  $100\mu\text{m} \times 100\mu\text{m}$  としている。

図より  $90\text{keV}$  あたりに明らかなピークが見られる。 $0 \sim 70\text{keV}$  あたりの分布は粒子のトラックが複数のピクセルにまたがって衝突したことによるものがほとんどで，バックグラウンドとなる。二次的な光子による Pair Monitor への寄与もわずかではあるがバックグラウンドとなる。これらのバックグラウンドは  $70\text{keV}$  以下をカットすることにより効率的に取り除ける。本研究回路においては外部から与えるスレッショルド電圧を  $70\text{keV}$  相当の電圧に設定することにより，バックグラウンドを取り除く。このとき，シリコン検出器は電子 1 個生成するために約  $3.6\text{eV}$  が必要になることを用いて，電圧に換算しスレッショルド電圧を設定する。また，3D ピクセル検出器のエネルギーデポジット量はほぼ厚さに比例すると考えられるので， $300\mu\text{m}$  の厚さのもと

でのシミュレーション結果を  $2/3$  倍し,  $200\mu m$  の下での値に換算する必要がある. 詳細については 4.3 節で述べる.

図 2.11: Pair Monitor でのエネルギー デポジットの分布 [16]

### 2.3 読み出し回路

ILCにおいてビームは高いルミノシティを得るために電子, 又は陽電子を束にしたバンチを約  $300ns$  間隔で 2820 個連ねて 1 トレインを構成し, これを  $5Hz$  で衝突させる. 個々のバンチは加速管内の加速電場により加速されるが, このとき加速電場はバンチ自身の作る電場の影響を受ける. そのため後続するバンチの加速に影響を与え, ビームを安定させる上で問題となる. そのため, トレイン内のバンチの状態をモニタし, それをもとに実時間で加速器の運転にフィードバックすることで, 安定したビームを供給する必要がある. Pair Monitorにおいてビームサイズを測定するためには, 先に述べたように高い位置分解能と時間分解能が検出器に要求される. 何故ならば位置分解能は  $r_{max}$  及び  $R_{pv}$  の精度に影響を与え, 時間分解能はトレインにおけるビームサイズ変化の情報量に影響を与えるためである. また, 位置分解能はセンサーのピクセルサイズによって決まり, 時間分解能はセンサーの電荷収集時間, 読み出し回路の時間分解能によって決まる. バンチごとのビーム情報を得られる時間分解能を有することが理想的ではあるが, そのためには 2820 個ものビーム情報を保持しておくレジスタが必要であり, 回路サイズの制限から本研究回路における達成は現実的ではない. 本研究回路においては  $0.87ms$  のトレインを 16 分割し, 16 分割されたそれぞれの時間領域に対して出力信号をレジスタに格納する. 回路構成の詳細については, 次章で述べる.

# 第3章 回路設計

## 3.1 回路の製作目的

図 3.1: ILC におけるビーム構造 [1]

1980 年代から、いくつかのリニアコライダー計画が世界で平行して進められてきたが、次期リニアコライダーの開発を一本化すべきとの声が高まり、2004 年夏の国際会議において、 $e^+e^-$  ビームの加速方式に超伝導技術を利用するリニアコライダーである ILC(International Linear Collider) が選択された。それまで、アジア地域では日本を中心としてビーム加速方式に常電導技術を用いる GLC ( Global Linear Collider) の研究開発を行っていたが、加速方式の変更と、それに伴うビームパラメータの変更により、従来のパラメータに最適化されていたリニアコライダー設計を新たなパラメータに最適化された設計に変更する必要がでてきた。GLC におけるビームパラメータに最適化された Pair Monitor からの読み出し回路の研究開発は既に行われていたが [17][18]、その回路を ILC におけるビームパラメータに最適化したものが本研究回路である。表 3.1 に従来の常電導方式のリニアコライダー (GLC) のビームパラメータと、超伝導方式のリニアコライダー (ILC) のビームパラメータを示した。また、図 3.2 にピクセル当たりの GLC 用のペアモニターからの読み出し回路 (以下、前研究回路と記す) の模式図を、図 3.3 に ILC 用の本研究回路の模式図を示した\*。

\*前研究回路ではマルチヒットを考慮しないため、OUTPUT 以降はコンパレータからの出力がローレベル、ハイレベルのどちらであるのかを判定できるだけの回路があればよい。一方、本研究回路ではマルチヒットを前提としているため、OUTPUT 以降でコンパレータからの出力を計数し、保持する機能を持ったデジタル回路が必要である。

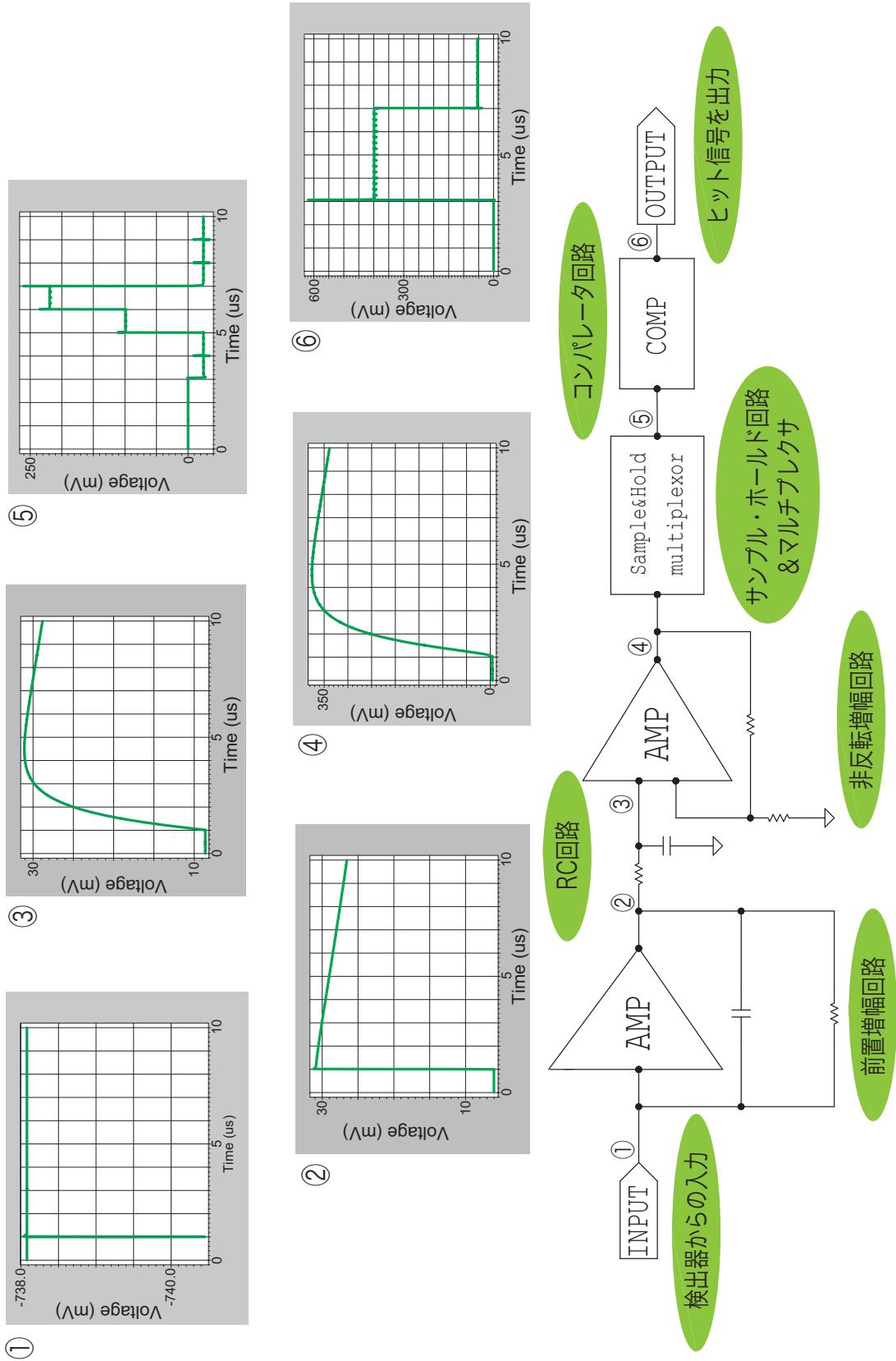

図 3.2: 前研究回路の模式図

図 3.3: 本研究回路の模式図

表 3.1: 常電導リニアコライダーと超伝導リニアコライダーのビームパラメータ

|              | 常電導方式 (GLC) | 超伝導方式 (ILC) |

|--------------|-------------|-------------|

| パンチ / トレイン   | 192         | 2820        |

| トレイン / 秒     | 150Hz       | 5Hz         |

| パンチ間隔        | 1.4ns       | 307.7ns     |

| トレインの長さ      | 269ns       | 0.847ms     |

| トレインとトレインの間隔 | 6.6ms       | 200ms       |

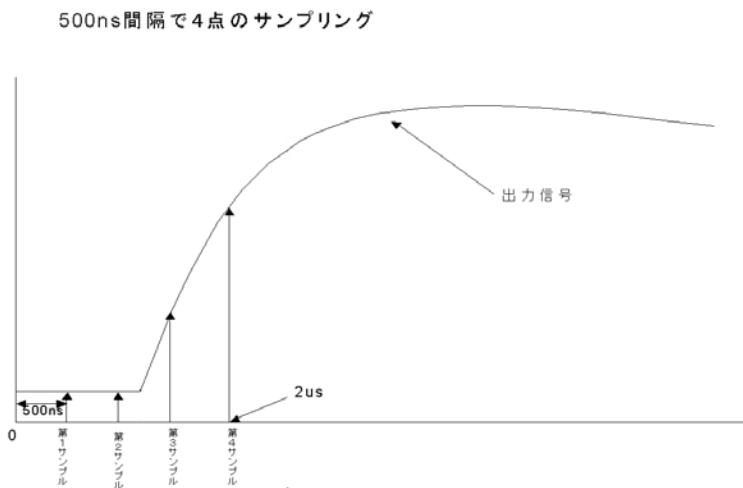

前章で述べたように、安定したビームを供給するためにはビーム形状を調べ、実時間で加速器の運転にフィードバックすることが必要であった。そして、ビーム形状を調べるために Pair Monitor を用いたのであった。前研究回路の回路方式で致命的であったのは、マルチヒットに対して信号の再構成ができない点である。ILC のビームパラメータにおいては 1 トレイン当たりのパンチ数が 2820 となっており、GLC のビームパラメータの値に比べて非常に大きくなっている。そのため、GLC のとき以上にマルチヒットの確率は上がってしまい、前研究回路の回路方式は使うことができなくなつた。そこで、ILC のビームパラメータに最適化した Pair Monitor からの読み出し回路の製作が必要になった。前研究回路はピクセルサイズが  $100\mu\text{m} \times 100\mu\text{m}$  であり、500ns 間隔で 4 点の信号をサンプリングすることにより、入射信号を再構成し入射時間、電荷量を求める方式であった。GLC のビームパラメータにおいては、パンチトレインの長さである 280ns を 4 等分する 70ns の時間分解能があれば、加速器の運転にフィードバックするために十分有用な情報が得られると考えられており、余裕を持たせて半分の 30ns 程度の時間分解能を目標としていた。また、二次粒子等のバックグラウンドを除くためには検出器通過時のエネルギー損失を求めればよく、そのエネルギー損失は電荷量の測定により求まる。そこで、電荷量を 10keV 以下の分解能で測定できることを目標としていた。図 3.4 は波形の 4 点サンプリングの概念図である。前研究回路の詳細については参考文献 [17], [18] を参照。

図 3.4: 前研究回路の波形の 4 点サンプル [18]

一方, 本研究回路はピクセルサイズが  $400\mu\text{m} \times 400\mu\text{m}$  であり, 一つのピクセルに対してマルチヒットが起こることを前提とし, バンチ間隔 307.7ns のダブルパルスを分離・区別できる時間分解能を目標としている. ピクセルサイズが前研究回路よりも大きくなった理由は, 全研究回路がマルチヒットの信号を再構成できなかったために, ピクセルサイズを小さくすることで, マルチヒットが起こる確率を下げていたこと, 及び, 本研究回路がデジタル・アナログ混載の回路であるために, 全研究回路よりも回路規模が大きくなり, 同じピクセルサイズに抑える回路設計の負担が大きいためである. バンチトレインの長さである 0.87ms を 16 等分し, それぞれの時間間隔におけるヒット数を計数・解析することでビーム情報を取得し, 実時間で加速器の運転にフィードバックをする. また, 二次粒子等のバックグラウンドを除くためには, アナログ波形をデジタル化するときのコンパレータにおいて適切なスレッショールド電圧を与えることでバックグラウンドによる計数を除くことができる.

表 3.2 に前研究回路と本研究回路の比較を示した.

表 3.2: 前研究回路と本研究回路との比較

|              | 前研究回路                                  | 本研究回路                                  |

|--------------|----------------------------------------|----------------------------------------|

| ピクセルサイズ      | $100\mu\text{m} \times 100\mu\text{m}$ | $400\mu\text{m} \times 400\mu\text{m}$ |

| ピクセル当たりのヒット数 | シングルヒットを想定                             | マルチヒットを想定                              |

| 時間分解能        | シングルパルスを 30ns の時間分解能で再構成               | ダブルパルスを 307.7ns の時間分解能で分離・区別           |

| バックグラウンド除去   | 電荷量の測定により除去                            | スレッショールド電圧の設定により除去                     |

Pair Monitor の検出器として用意される 3D シリコンピクセル検出器は, その製造上の便宜から  $200\mu\text{m}$  程度の厚みを有するものを想定している. そうすると, 典型的な信号スケールは 15000 電子相当と見積もることができる. したがって、雑音レベルを 1000 電子相当とし, コンパレータのスレッショールドを 2000 電子相当に設定すれば, 電子回路上は, noise-free な計測環境が実現できると考える. また, 3D ピクセルセンサーは, その構造上, 信号極性を自由に選択して実装することが可能である. しかし, 両方の極性に対応するように回路を構成すると, 頑雑になる上に, それぞれの極性について同等の性能を確保することは, 追加的な設計負担が発生すると考えられる. そこで, 今回の試作においては, 負電荷入力の回路として構成することにする.

さらに, 信号電荷は, 最小間隔 300ns で発生するので, 増幅器の立ち上がり時間は, 100ns 程度に設定し, その後速やかにベースラインに復帰するような構成をとることが必要である. そこで, 本設計では定電流帰還によるベースライン復帰方式を採用することとする. こうすることによって, RC 時定数による回路構成に比較して高速な波形整形を実現することができる.

こうして生成された増幅器の出力信号は, コンパレータ(差動スレッショールド)によってデジタル(CMOS フルスウィング信号)化され, その数をカウンタ回路によって計数し, ラッチ回路に記録される. 表 3.3 に本研究回路の要求水準を示した.

表 3.3: 本研究回路の要求水準

|             |            |

|-------------|------------|

| 典型的信号スケール   | 15000 電子相当 |

| 雑音レベル       | 1000 電子相当  |

| スレッショールドレベル | 2000 電子相当  |

| 入力信号極性      | 負電荷        |

| 增幅器立ち上がり時間  | 100ns      |

| ダブルパルス分解時間  | 300ns      |

| 帰還方式        | 定電流帰還方式    |

| コンパレータ      | 差動スレッショールド |

## 3.2 回路概観

図 3.5: 回路概観

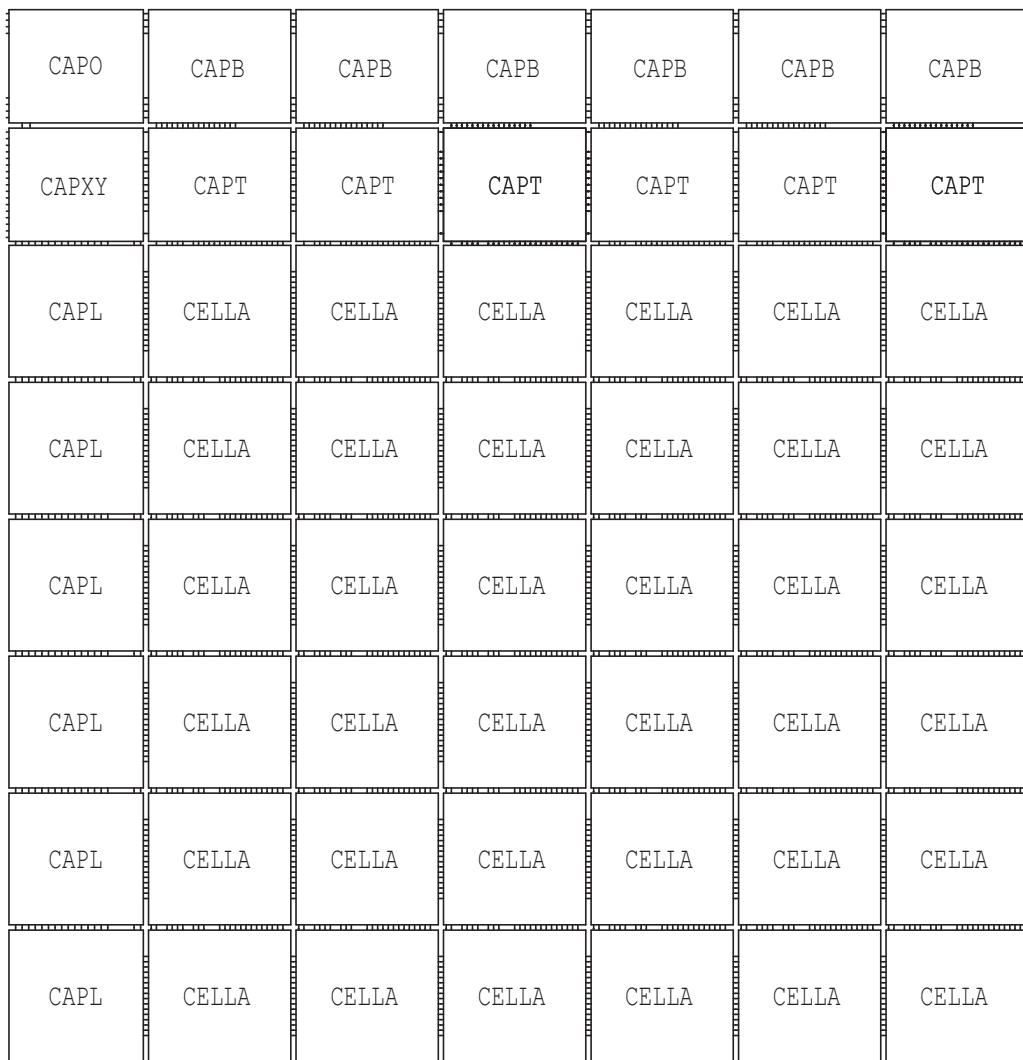

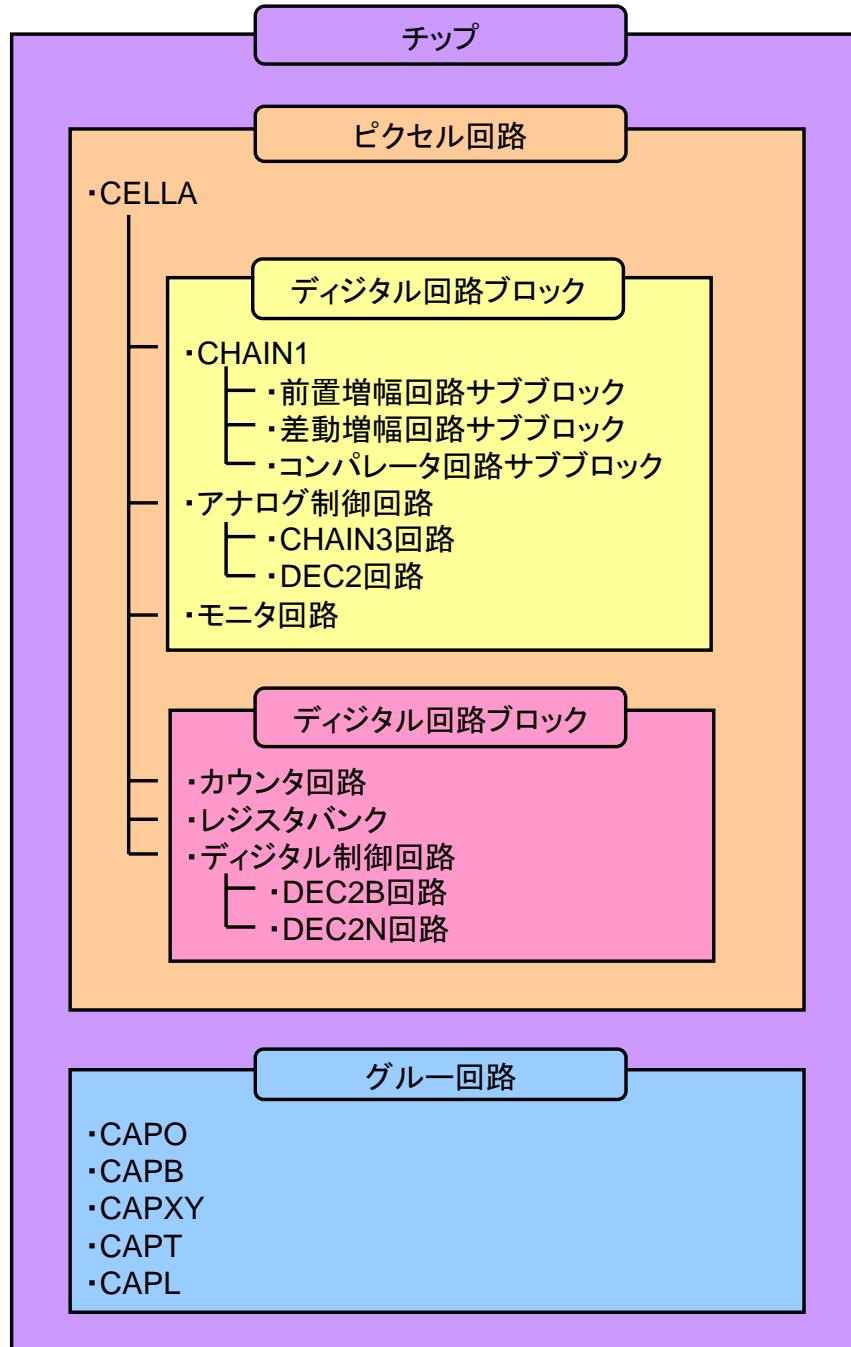

図 3.5 に本研究回路の概観を示した。本回路は CELLA 回路が横方向に 6 個、縦方向に 6 個並んだアレイ構造をしており、その外側に横方向に 6 個の CAPT 回路、及び CAPB 回路、縦方向に 6 個の CAPL 回路、さらに CAPO 回路と CAPXY 回路それぞれ 1 個ずつから構成されている。それぞれの CELLA が一つのピクセルに対応している。CAPT、CAPB、CAPL、CAPO、CAPXY 回路はピクセル回路を統合して集積回路としてまとまった動作をするために必要な周辺回路であるグレー回路を構成している。図 3.6 に回路の階層構造を示した。以下、それぞれの階層について詳述する。

図 3.6: 回路の階層構造

### 3.3 ピクセルごとの回路構成

図 3.7 にピクセルごとの回路構成を示した。ピクセルごとの回路ブロックは、さらにアナログ回路部とデジタル回路部からなる。アナログ回路部の役割は検出器の電気信号を増幅し、デジタル化することであり、デジタル回路部の役割はアナログ回路部でデジタル化された信号を計数・保持することである。各部の機能等については、以下で詳述している。

### 3.4 アナログ回路部の構成

図 3.8: アナログ回路部の構成

図 3.8 にアナログ回路部の回路構成を示した。アナログ回路部の構成は以下の通りである。

- 検出器からの信号が入力され、その信号を増幅し外部から与えられるスレッショールド電圧以上の増幅信号をコンパレータでデジタル化する CHAIN1 回路

- CHAIN1 回路の信号を 3 つのチャンネルで観測できるモニタ回路

- テストパルスイネーブル信号、ピクセル選択信号、及びモニタのチャンネルを選択するための信号の制御回路

それぞれの回路についての詳細を以下で記述する。

### 3.4.1 CHAIN1 回路

図 3.9: CHAIN1 回路のシンボル(上)とその内部構成(下)

表 3.4: CHAIN1 回路の素子・端子の機能

| 素子・端子名         | 機能          |

|----------------|-------------|

| FB4            | 帰還要素        |

| PrC2           | 増幅要素        |

| SW1            | テストパルス用スイッチ |

| ACC            | 自動電流制御要素    |

| DIFA           | 差動増幅要素      |

| COMP0          | コンパレータ      |

| INV1S          | インバータ       |

| AIN            | 検出器からの入力    |

| TP             | テストパルス入力    |

| TPENB          | テストパルスイネーブル |

| RB             | ACC 回路のスイッチ |

| ADC,BDC        | スレッショールド用電圧 |

| VH1,VH2,VH3    | 2.5V 基準電圧   |

| VM1            | 1.25V 基準電圧  |

| VL1,VL2,VL3    | 0V 基準電圧     |

| DOUT           | CHAIN1 の出力  |

| MON1,MON2,MON3 | モニタ用出力      |

CHAIN1 回路の役割は検出器から入ってくる信号を前置増幅回路サブブロックと差動増幅回路サブブロックの 2 段で増幅させ、コンパレータ回路サブブロックにおいて外部から設定したスレッショールド電圧以上の増幅信号をデジタル信号に変換することである。以下では、それぞれのサブブロックにおける、より詳細な回路機能の説明と、そこでのインプット波形、及びアウトプット波形を示す。

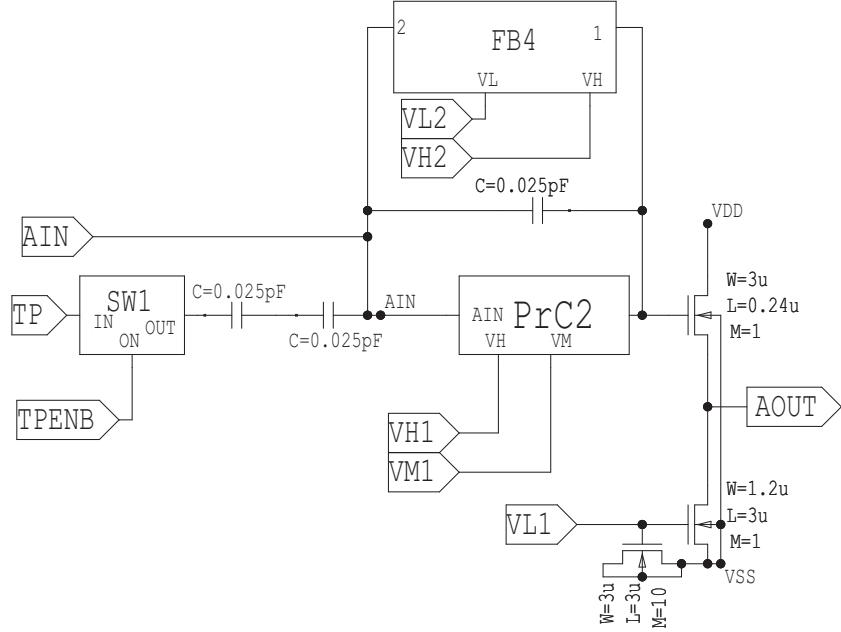

### 前置増幅回路サブブロック

図 3.10: 前置増幅回路サブブロック

前置増幅回路サブブロックは、負電荷極性である入力電荷を積分し電圧で出力する反転型の荷電増幅器であり、テストパルス用のスイッチ SW1、増幅要素 PrC2、帰還要素 FB4、0.025 pF の帰還容量、及びソースフォロア回路とから構成されている。FB4 は、定電流帰還による直流帰還回路であって、前置増幅器の出力信号を 300 ns 以内にベースラインまで復帰させることができるようになっている。SW1 は TPENB がハイレベルのときに TP を前置増幅回路に流す。このときパルス電圧である TP は、コンデンサにより模擬的な電荷インパルスとなって回路に入り、その電荷量は  $Q = CV$  ( $C: 0.125[pF]$  コンデンサ容量、 $V: TP$  のパルス電圧) で表される。AIN には検出器からの信号が入るが、検出器の energy deposit を  $E[eV]$  とすると入力電荷は

$$Q[C] = \frac{eE}{W} \quad (3.4.1)$$

となる。ここで、 $e$  は電気素量  $1.6 \times 10^{-19}[C]$ 、 $W$  は電子 1 個を遊離させるのに必要なエネルギーであり、シリコン検出器においては  $3.6[eV]$  である。ソースフォロア回路は入力電圧と出力電圧が等しい回路であるが、入力インピーダンスが高く、出力インピーダンスが低いことが特徴である。そのため、ソースフォロア回路をはさんだ前後の回路は、互いにおよぼす影響を弱めることができる。前置増幅器サブブロックに

続く差動増幅回路サブブロックにおける ACC 回路のスイッチ (RB) を動かしたときの影響を弱め、ドライブ能力を高めることができることが本ソースフォロア回路の役割である。

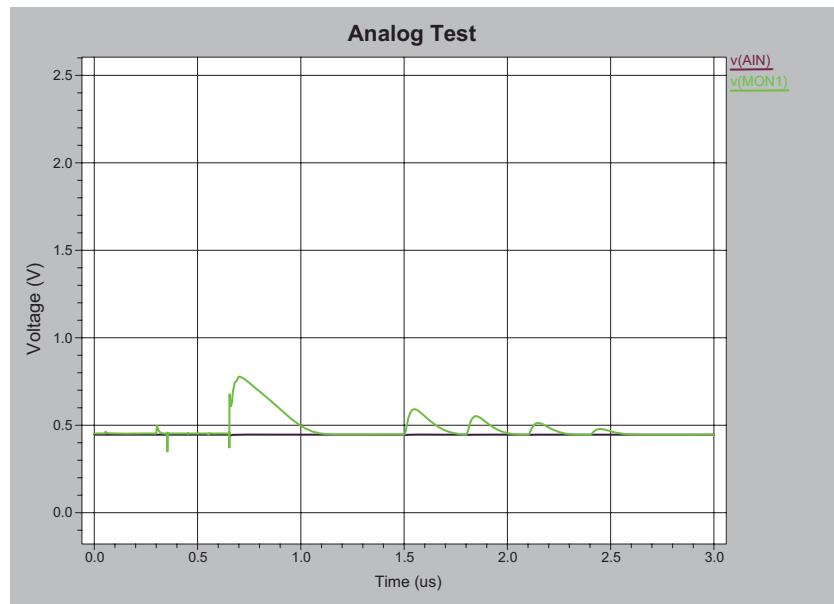

図 3.11 は入力電荷インパルス波形 ( $v(AIN)$ )、図 3.12 は入力電荷インパルス ( $v(AIN)$ )、及び前置増幅回路からの出力波形 ( $v(MON1)$ ) を示した図である。1500ns に 31250 電子相当、1800ns に 23438 電子相当、2100ns に 15625 電子相当、2400ns に 7813 電子相当の負電荷インパルスが連続して入力されている。なお、1200ns より前に差動増幅回路のリセットスイッチやテストパルス用のスイッチが切り替わったことによる影響が見られる。

図 3.11: 前置増幅回路の入力信号

図 3.12: 前置増幅回路の入力信号 ( $v(AIN)$ ) と出力信号 ( $v(MON1)$ )

### 差動増幅回路サブブロック

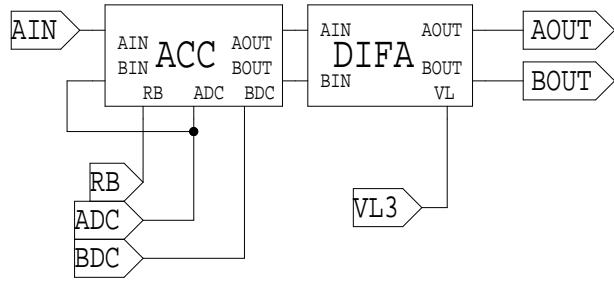

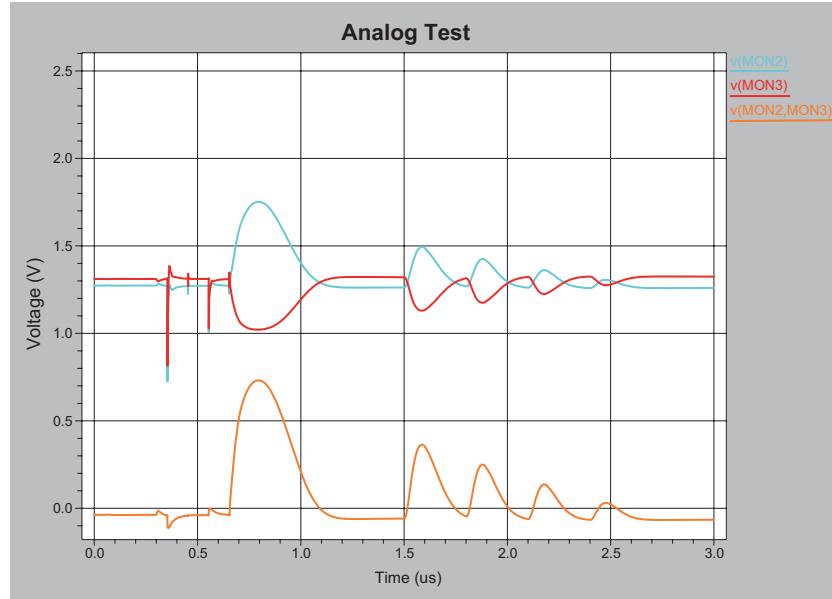

図 3.13: 差動増幅回路サブブロック

差動増幅回路サブブロックは、自動電流制御要素 ACC 及び差動増幅要素 DIFA から構成されている。ACC 回路は AC 結合によって前段との直流を切るとともにコンパレータ回路のためのスレッショールドを与えており、前段との直流を切るのは前段の信号が温度条件などによってゆれたときの影響を小さくするためである。RB は ACC 回路のスイッチとなっていて、RB がハイレベルのときに ACC 回路は動作する。RB がローレベルのときには ADC と AOUT, BDC と BOUT がそれぞれ短絡し、ACC 回路は動作しない。DIFA 回路は ACC 回路からの信号を増幅している。増幅率は基準電位 VL3 によって決まる。

図 3.14 は差動増幅回路の出力信号  $v(MON2)$  と  $v(MON3)$ 、及び、それらの信号の差の波形 ( $v(MON2,MON3)$ ) を示した図である。ここで、MON2 と MON3 のベースラインの電位差が、次段のコンパレータ回路のスレッショールド電圧になる。

図 3.14: 差動増幅回路の出力信号 ( $v(MON2), v(MON3)$ ) とそれらの差をとった波形 ( $v(MON2,MON3)$ )

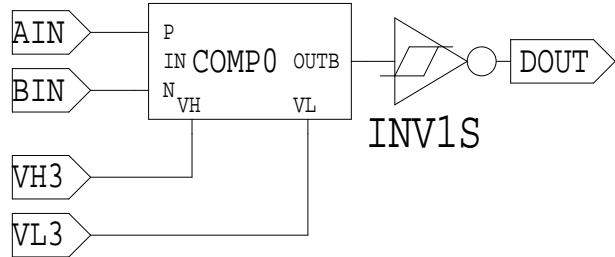

## コンパレータ回路サブブロック

図 3.15: コンパレータ回路サブブロック

コンパレータ回路サブブロックは、コンパレータ回路 (COMP0) とシュミットトリガー機能を備えたインバータ回路 INV1S とから構成されている。コンパレータは差動スレッショルドのコンパレータであり、スレッショルド電圧は、AIN と BIN のベースラインの電位差に相当する。AIN と BIN の電位差がスレッショルド電圧を超えると、2.5V のデジタル信号を出力する。ここで、ベースラインの電位差は差動增幅回路ブロックの ACC 回路に入力される ADC と BDC の電位差に比例する。つまり、ADC と BDC がコンパレータのスレッショルド電圧を決めている。比例定数は DIFA 回路の増幅機能に依存する。INV1S はコンパレータの出力波形を反転させるとともに、シュミットトリガー機能により波形を整える。これは、スレッショルドの近傍でのイレギュラーな動作を防止するのに役立つ。

図 3.16 はコンパレータ回路の出力信号  $v(\text{CMPDOUT})$  と差動增幅回路からの出力 AIN と BIN の差をとった波形 ( $v(\text{MON2,MON3})$ ) を示した図である。AIN と BIN の差 ( $v(\text{MON2,MON3})$ ) が 0V を超えたところでコンパレータが動作している様子が確認できる。

図 3.16: コンパレータ回路の出力信号  $v(\text{CMPDOUT})$  と差動增幅回路からの出力の差をとった波形 ( $v(\text{MON2,MON3})$ )

### 3.4.2 アナログ制御回路

図 3.17: アナログ制御回路

表 3.5: アナログ制御回路の素子・端子の機能

| 素子・端子名   | 機能                  |

|----------|---------------------|

| EDFFP    | フリップ・フロップ           |

| TRBUF    | トライステートバッファー        |

| NANDP    | NAND 素子             |

| 1P,4P    | インバータ               |

| XSEL     | XSEL 信号入力端子         |

| YSEL     | YSEL 信号入力端子         |

| WR       | フリップ・フロップイネーブル入力    |

| DIN      | フリップ・フロップへのデータ入力    |

| CK       | フリップ・フロップ同期信号入力     |

| INIT     | フリップ・フロップのリセットスイッチ  |

| SELB     | SELB 信号出力           |

| SEL      | SEL 信号出力            |

| TPENB    | テストパルスイネーブル出力       |

| DOUT     | テストパルスイネーブルチェック信号出力 |

| S0,S1,S2 | モニタチャンネル選択信号出力      |

図 3.17 にアナログ制御回路の回路構成を示した。CHAIN1 回路内の波形観測点を選択するための信号 (S0, S1, S2), ピクセル選択信号 (SEL, SELB), 及びテストパルス信号を制御する TPENB 信号を出力する。

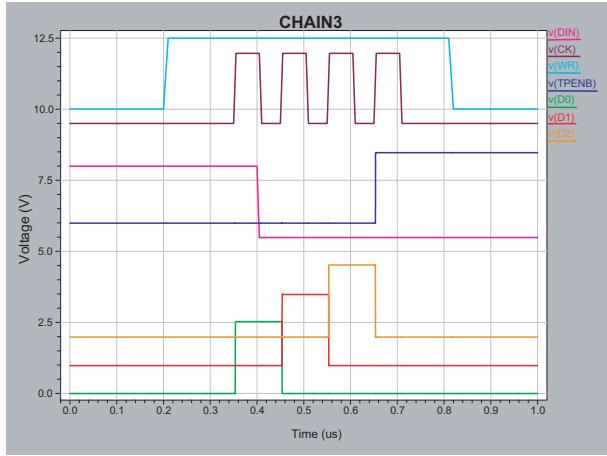

### CHAIN3 回路

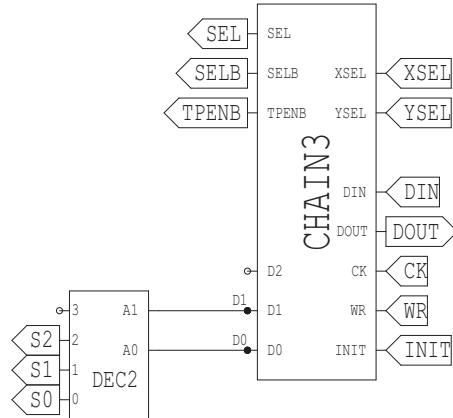

図 3.18: CHAIN3 回路のシンボル(左)とその内部構成(右)

図 3.18 は CHAIN3 回路の回路構成を示しており、イネーブルデータ端子付フリップ・フロップ、トライステートバッファー、インバータ、及び NAND 回路とから構成されている。D0, D1 は次段の DEC2 回路において、CHAIN1 回路内の波形観測点を選択するための信号を生成するための信号である。D2 は本回路においては使用されない出力である。TPENB はテストパルスイネーブル信号であり、CHAIN1 回路において TPENB がハイレベルのときにテストパルスを回路内に流す。DOUT は TPENB 信号のレベルをチェックするための出力信号であり、TPENB と同じ信号レベルを出力する。SEL はピクセル選択用の信号であり、選択されているピクセルにおいては信号レベルがハイレベルとなっている。また、複数のピクセルにおいて SEL 信号が同時にハイレベルとなることはない。WR は SEL がハイレベルのピクセル(選択されているピクセル)において、フリップフロップのイネーブル信号となり、信号レベルがハイレベルのときにのみフリップ・フロップが動作する。CK はフリップフロップのクロック信号であり、信号レベルがハイレベルになるときにフリップ・フロップの状態に合わせてフリップ・フロップの出力を変化させる。INIT はフリップ・フロップのリセットスイッチであり、信号レベルがハイレベルのときにフリップフロップの出力がローレベルになる。

図 3.21, 図 3.23, 図 3.25 はそれぞれ CHAIN1 回路の MON1, MON2, MON3 の出力波形をモニタするための CHAIN3 回路のセットアップを示した図である<sup>†</sup>。

<sup>†</sup>図 3.21, 図 3.23, 図 3.25 中の信号は全て 0V ~ 2.5V のデジタル信号である。波形が重なると分かれにくいため、0V 電圧をずらして示してある。また、信号入力のタイミングは図に示したとおりである。

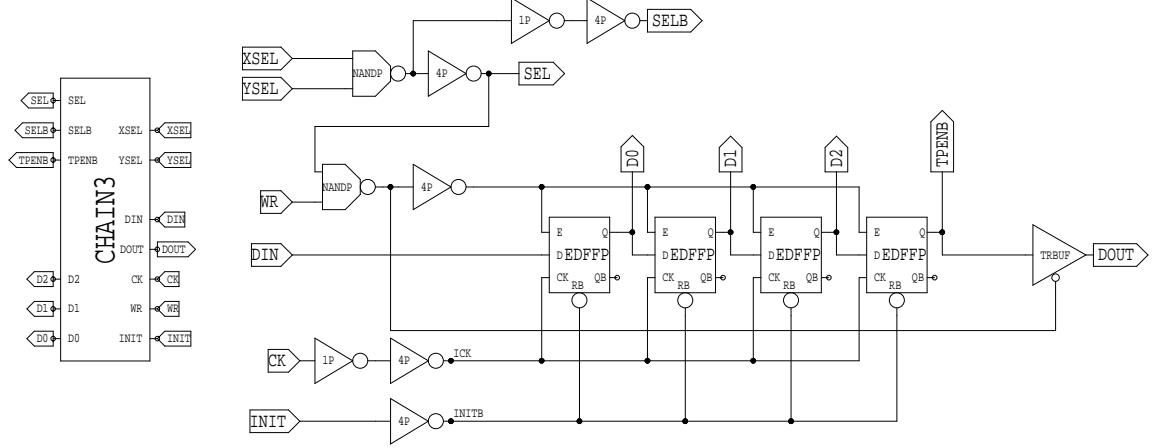

## DEC2 回路

図 3.19: DEC2 回路のシンボル (左) とその内部構成 (右)

表 3.6: DEC2 の真理値表

| input |    | output |    |    |    |

|-------|----|--------|----|----|----|

| A0    | A1 | Q0     | Q1 | Q2 | Q3 |

| 0     | 0  | 1      | 0  | 0  | 0  |

| 0     | 1  | 0      | 0  | 1  | 0  |

| 1     | 0  | 0      | 1  | 0  | 0  |

| 1     | 1  | 0      | 0  | 0  | 1  |

図 3.19 は DEC2 回路の回路構成を示しており、インバータと AND 回路とから構成される。CHAIN1 回路内波形のモニタチャンネル選択用デコーダである。Q0, Q1, Q2 はそれぞれ CHAIN1 回路の MON1, MON2, MON3 の出力波形をモニタするための信号であり、A0, A1 の組み合わせで Q0, Q1, Q2 の出力が変化する。表 3.6 に真理値表が示してある。Q3 は本回路においては使用されない出力である。

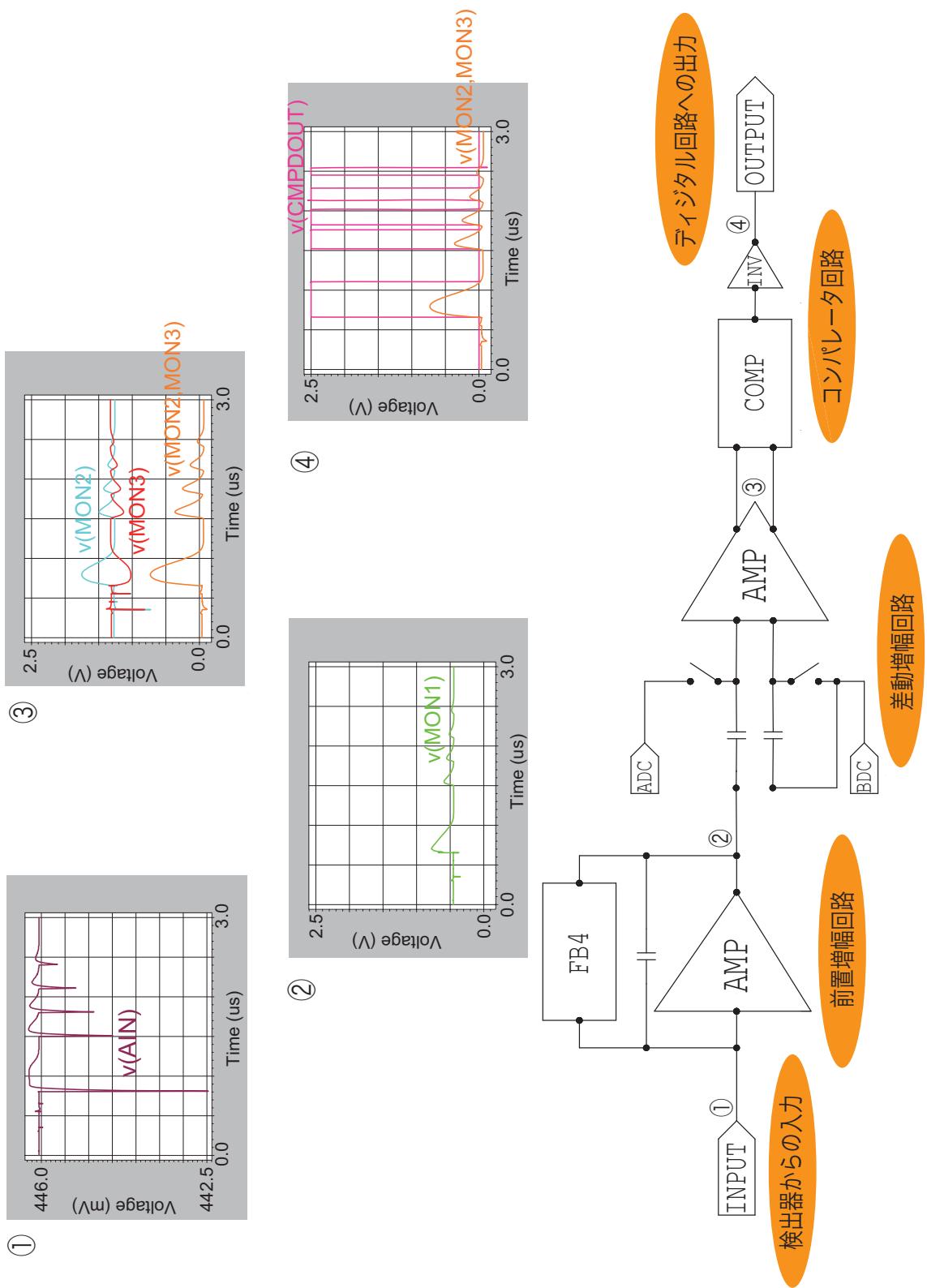

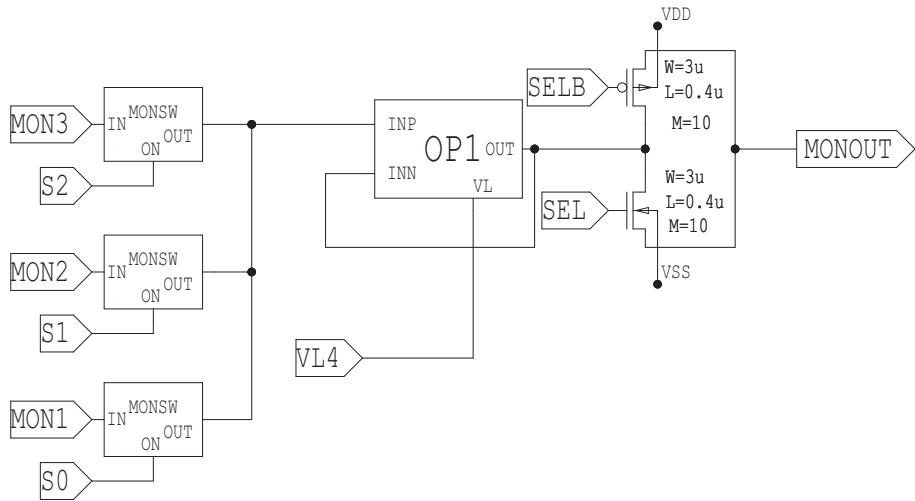

### 3.4.3 モニタ回路

図 3.20: モニタ回路

表 3.7: モニタ回路の素子・端子の機能

| 素子・端子名         | 機能               |

|----------------|------------------|

| OP1            | 増幅要素             |

| MONSW          | モニタチャンネル選択スイッチ   |

| MON1,MON2,MON3 | CHAIN1 の観測点からの信号 |

| S0,S1,S2       | モニタチャンネル選択信号     |

| SEL,SELB       | ピクセル選択信号         |

| VL4            | 0V 基準電圧          |

| MONOUT         | モニタ回路の出力         |

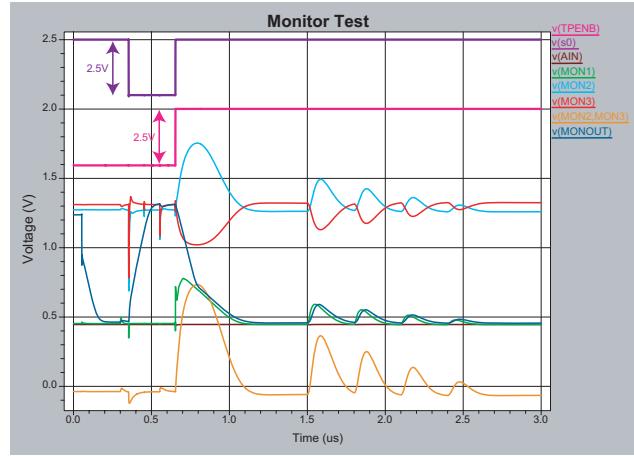

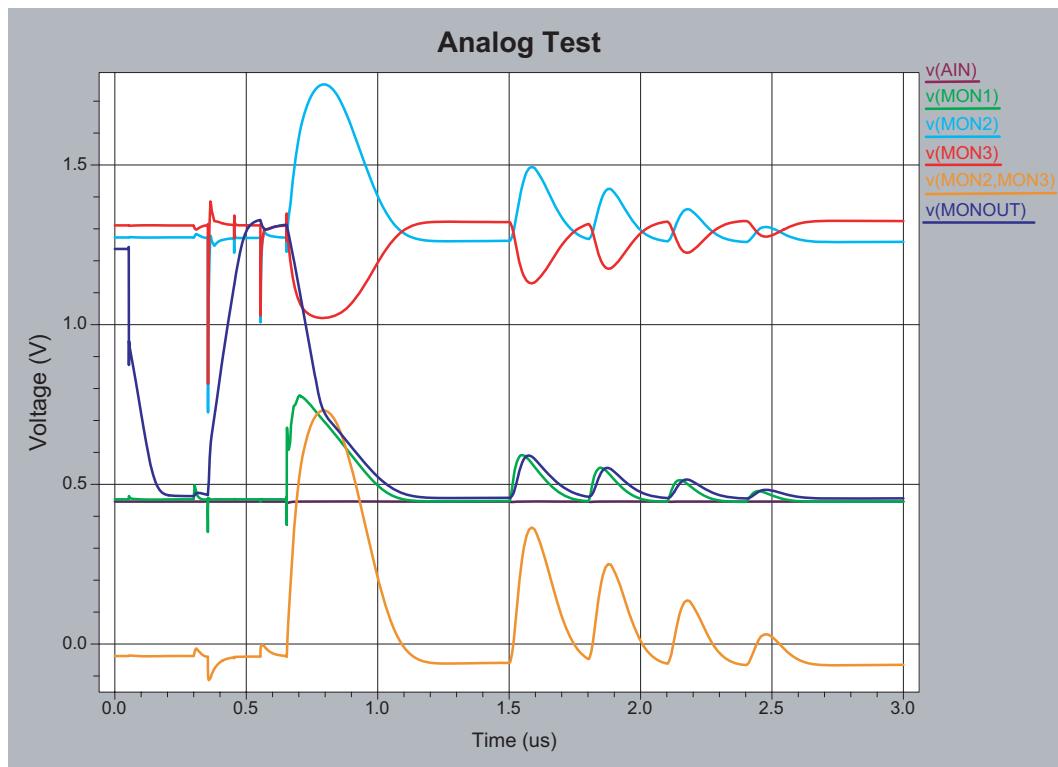

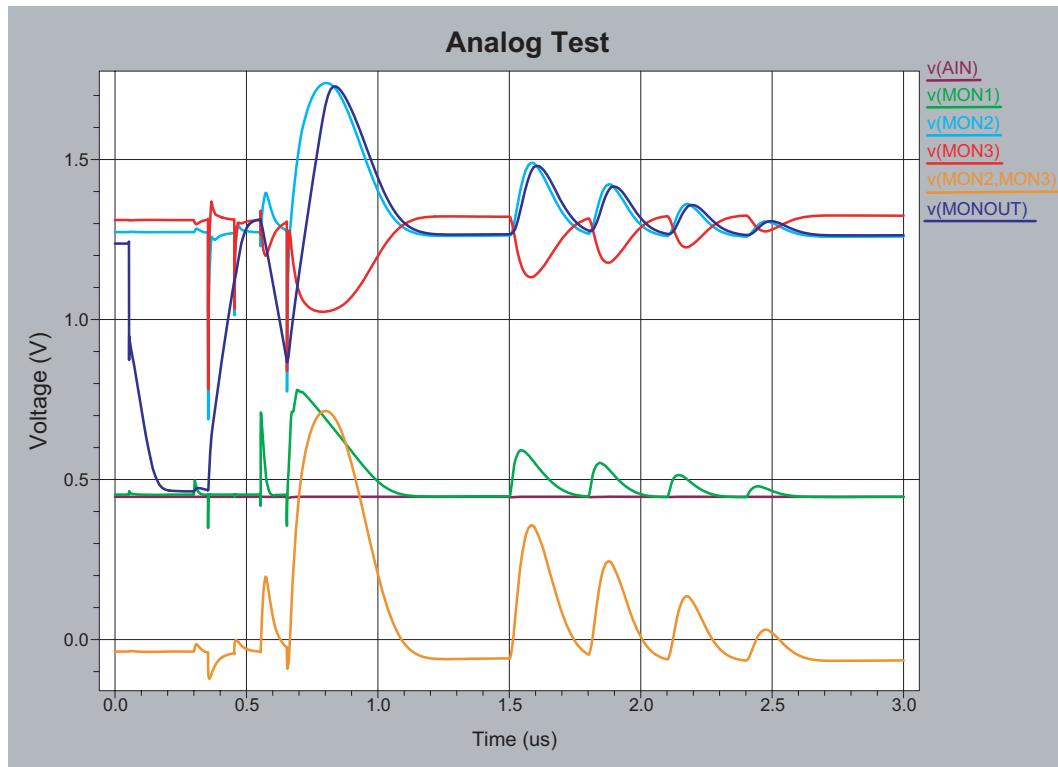

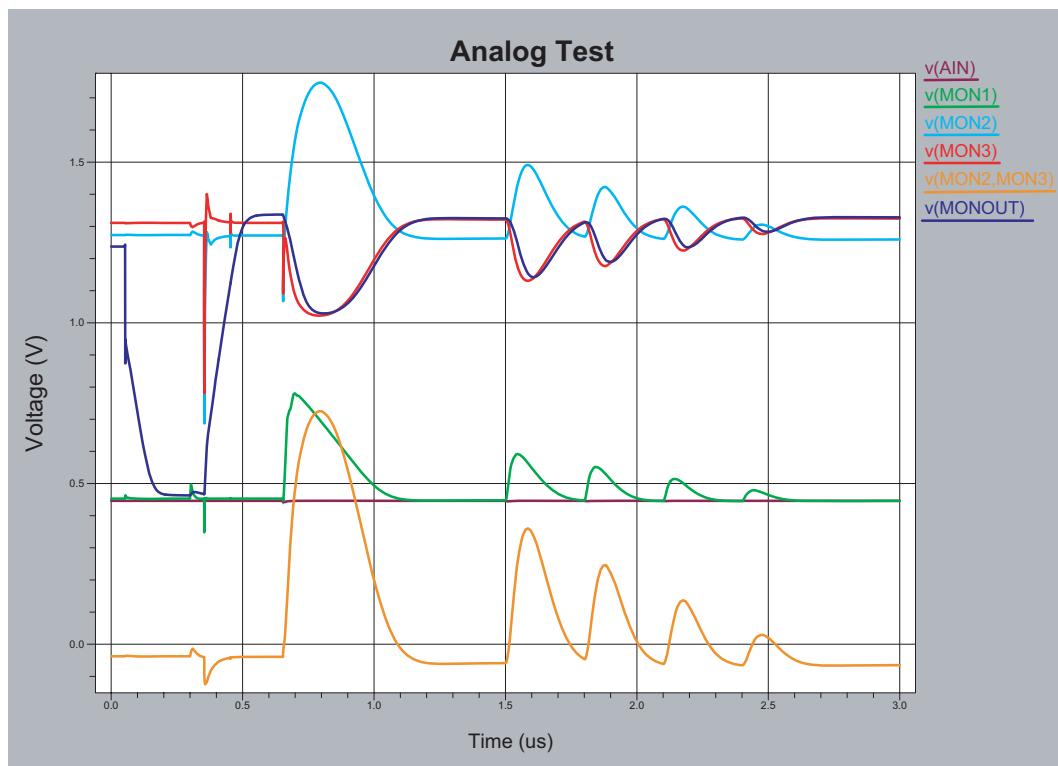

図 3.20 にモニタ回路の回路構成を示した。SEL, SELB は選択されているピクセルを示す信号であり, SEL がハイレベル (SELB がローレベル) のときにはピクセルが選択されていて, SELB がハイレベル (SEL がローレベル) のときにはピクセルが非選択であることを示す。VL4 は 0V 基準電位で OP1 の動作に必要である。OP1 は増幅要素であり, ユニティーゲイン・バッファの回路構成をとってノイズをキャンセルする役割を担っている。MON1 は CHAIN1 回路の前置増幅器サブブロックの出力信号, MON2, MON3 は差動増幅回路サブブロックの出力信号である。S0, S1, S2 は MONSW のスイッチであり, スイッチ信号がハイレベルとなっている MONSW に入力している MON1, MON2, MON3 のいずれかが MONOUT として出力される。

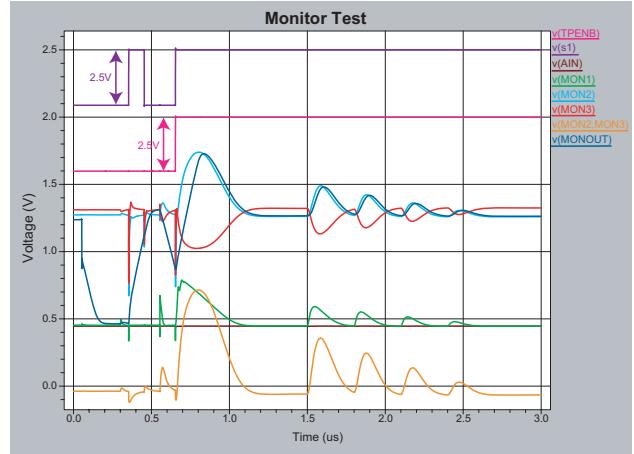

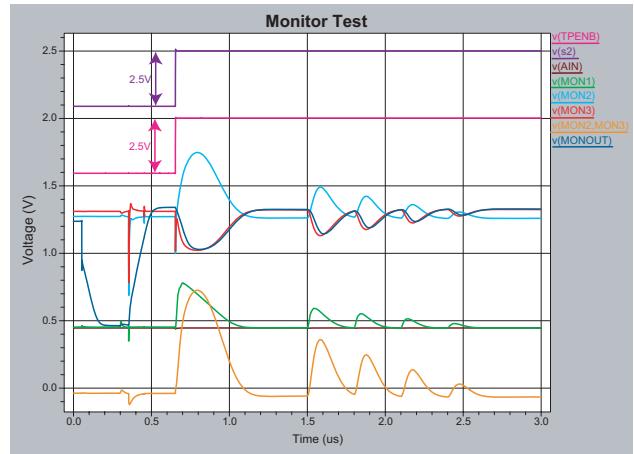

図3.22,図3.24,図3.26はそれぞれMON1,MON2,MON3の信号をMONOUTとして出力したものである<sup>‡</sup>. S0,S1,S2の信号レベルが確定してからはMON1,MON2,MON3の信号がモニタ回路から波高,及び時間分解能が十分な精度で観測されていることが分かる. なお,700ns当たりの信号はTPENB信号がローレベルからハイレベル

<sup>†</sup>2.5V デジタル信号の TPENB 信号の出力と S0 , S1 , S2 信号の波形が重なってしまうので , それらの信号の波形をずらして示している .

ルになるときの雑音信号が増幅されたものである。このため、計測はこの雑音がベースラインまで復帰してから開始する必要がある。

図 3.21: MON1 出力波形モニタ用信号

図 3.22: モニタ回路で MON1 の波形を観測

図 3.23: MON2 出力波形モニタ用信号

図 3.24: モニタ回路で MON2 の波形を観測

図 3.25: MON3 出力波形モニタ用信号

図 3.26: モニタ回路で MON3 の波形を観測

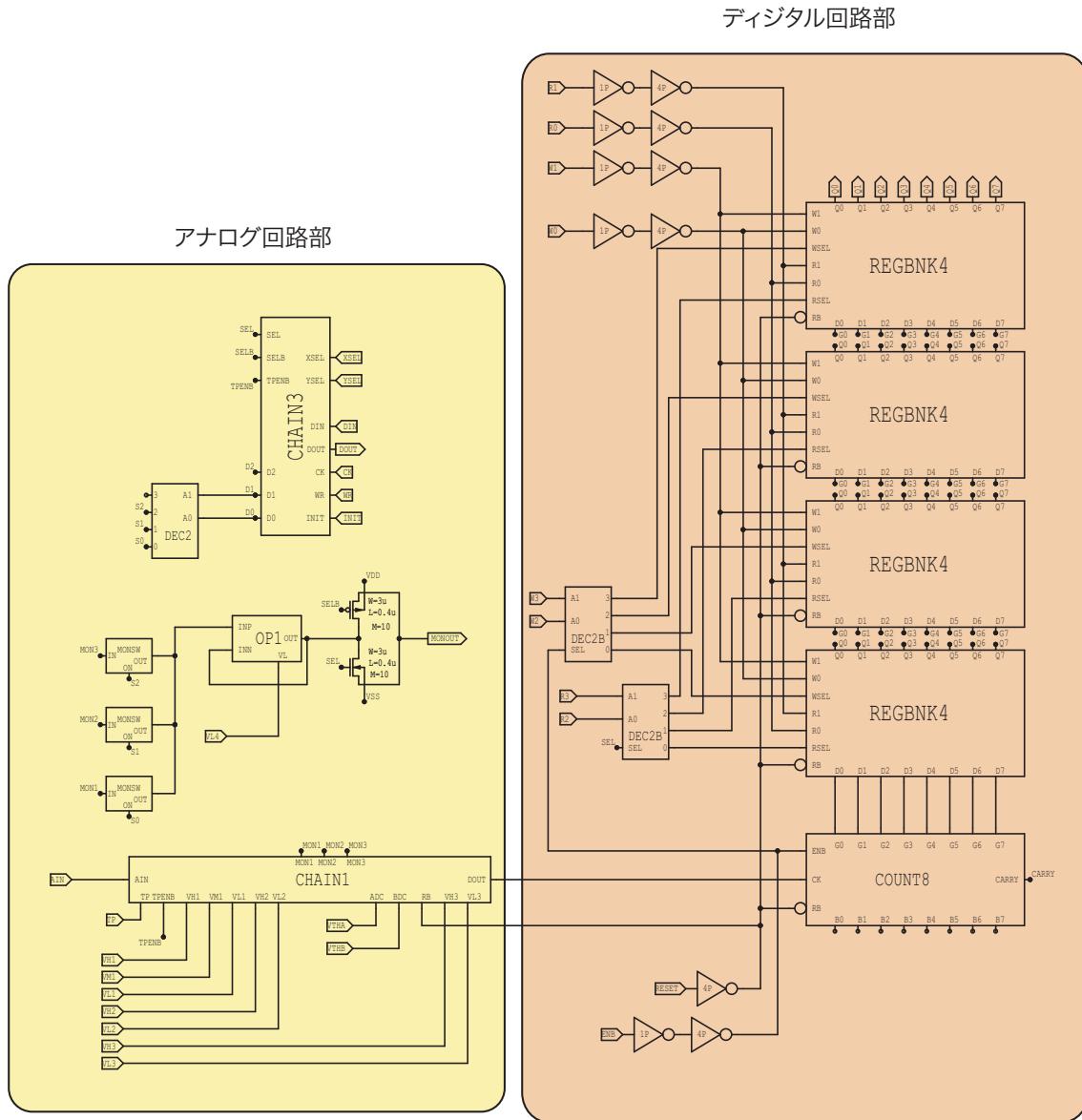

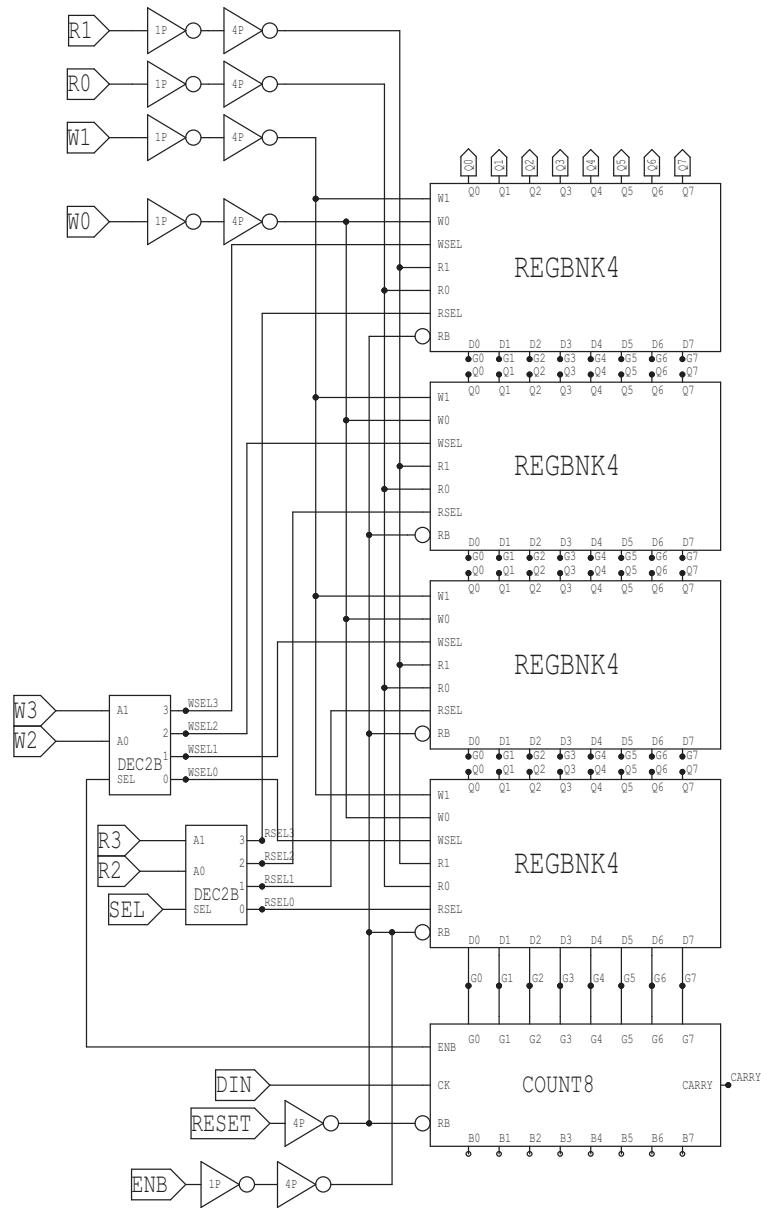

### 3.5 ディジタル回路の構成

図 3.27: ディジタル回路の構成

図 3.27 にデジタル回路部の回路構成を示した。デジタル回路の構成は以下の通りである。

- CHAIN1回路からのデジタル出力信号をグレイコードで計数するカウンタ回路

- 計数値を保持するレジスタバンク

- レジスタを選択するための制御回路

それぞれの回路についての詳細を以下で記述する。

### 3.5.1 COUNT8 回路

図 3.28: COUNT8 回路のシンボル(左)とその内部構成(右)

表 3.8: COUNT8 回路の素子・端子の機能

| 素子・端子名                  | 機能                    |

|-------------------------|-----------------------|

| EDFFP                   | フリップ・フロップ             |

| COUNT4                  | 4bit カウンタ             |

| ENB                     | イネーブル信号               |

| CK                      | 入力クロック信号              |

| RB                      | リセット信号                |

| CARRY                   | キャリー信号(本回路においては使用しない) |

| B0,B1,B2,B3,B4,B5,B6,B7 | 通常の2進コード出力信号          |

| Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7 | グレイコード出力信号            |

図 3.28 は COUNT8 の回路構成を示しており、COUNT4 回路、フリップ・フロップ、インバータとから構成される。COUNT8 回路は CHAIN1 回路からのデジタル出力信号をグレイコードで計数する 8bit の 2 進カウンタ回路である。COUNT4 は 4bit の 2 進カウンタであり、並列に接続された 2 つの COUNT4 を同期させることにより 8bit の計数が可能になる。ENB 信号がハイレベルの状態のときに CHAIN1 からのデジタル信号をカウントする。RB 信号はリセット信号であり、RB 信号がハイレベルになるとカウンタの計数値がリセットされる。B0, B1, B2, B3, B4, B5, B6, B7 のそれぞれは通常の 2 進コードを表す信号であり、信号のハイレベルは 1、ローレベルは 0 を表す。B0 ~ B7 が通常の 2 進数の 1bit ~ 8bit にそれぞれ対応している。Q0, Q1, Q2, Q3, Q4, Q5, Q6, Q7 のそれぞれはグレイコードの 2 進コードを表す信号であり、信号のハイレベルは 1、ローレベルは 0 を表す。Q0 ~ Q7 がグレイコードの 2 進数の 1bit 枠 ~ 8bit 枠にそれぞれ対応している。本回路においては COUNT8 回路を Q0 ~ Q1 を使用するグレイコードカウンタとして用いる。通常の 2 進コードでは 0111 の次は 1000 という具合に 1 を加えることにより、多くの文字が同時に変化する場合があるが、グレイコードでは必ず 1 文字しか変化しない。そのため、2 進コードのカウ

ンタでは検出器からの 1 つのデジタル信号を計数するときに、複数の桁が同時に変わった瞬間の出力を読み込んでしまったレジスタバンクは、とんでもなく違った値に解釈してしまう恐れがあるが、グレイコードを用いたカウンタでは誤差を高々 1 カウントに抑えることができる。

表 3.9: 4 ビット数の 2 進コードとグレイコードの対応表

| 数  | 2 進コード  | グレイコード  |

|----|---------|---------|

| 0  | 0 0 0 0 | 0 0 0 0 |

| 1  | 0 0 0 1 | 0 0 0 1 |

| 2  | 0 0 1 0 | 0 0 1 1 |

| 3  | 0 0 1 1 | 0 0 1 0 |

| 4  | 0 1 0 0 | 0 1 1 0 |

| 5  | 0 1 0 1 | 0 1 1 1 |

| 6  | 0 1 1 0 | 0 1 0 1 |

| 7  | 0 1 1 1 | 0 1 0 0 |

| 8  | 1 0 0 0 | 1 1 0 0 |

| 9  | 1 0 0 1 | 1 1 0 1 |

| 10 | 1 0 1 0 | 1 1 1 1 |

| 11 | 1 0 1 1 | 1 1 1 0 |

| 12 | 1 1 0 0 | 1 0 1 0 |

| 13 | 1 1 0 1 | 1 0 1 1 |

| 14 | 1 1 1 0 | 1 0 0 1 |

| 15 | 1 1 1 1 | 1 0 0 0 |

### 3.5.2 REGBNK4 回路

表 3.10: REGBNK4 回路の素子・端子の機能

| 素子・端子名                  | 機能                     |

|-------------------------|------------------------|

| DEC2B                   | 書き込む LATCH8 を選択するデコーダ  |

| DEC2N                   | 読み込む LATCH8 を選択するデコーダ  |

| LATCH8                  | COUNT8 の計数値を記録するラッチ回路  |

| W1,W0                   | 書き込む LATCH8 を選択するための信号 |

| WSEL                    | DEC2B のセレクト信号          |

| R1,R0                   | 読み込む LATCH8 を選択するための信号 |

| RSEL                    | DEC2N のセレクト信号          |

| RB                      | 記録されている値のリセット信号        |

| D0,D1,D2,D3,D4,D5,D6,D7 | 入力信号                   |

| Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7 | 出力信号                   |

図 3.29: REGBNK4 回路のシンボル (左) とその内部構成 (右)

図 3.29 は REGBNK4 回路の回路構成を示しており, LATCH8, DEC2N, DEC2B, インバータとから構成される。LATCH8 は 8bit のラッチ回路であり, COUNT8 回路の計数値を記録する。DEC2B は COUNT8 回路の計数値を書き込む LATCH8 を選択するためのデコーダである。WSEL がハイレベルの状態で動作し, W0, W1 に依ってどの LATCH8 に書き込むかを選択する。選択された LATCH8 に COUNT8 からの入力信号 D0~D7 が記録される。DEC2N は COUNT8 回路の計数値を読み出す LATCH8 を選択するためのデコーダである。RSEL がハイレベルの状態で動作し, R0, R1 に依ってどの LATCH8 から読み込むかを選択する。選択された LATCH8 の Q0~Q7 が読み出される。

### 3.5.3 DEC2B 回路

図 3.30: DEC2B 回路のシンボル (左) とその内部構成 (右)

表 3.12: DEC2B の真理値表

表 3.11: DEC2B 回路の素子・端子の機能

| 素子・端子名         | 機能     |

|----------------|--------|

| A1, A2         | 入力信号   |

| SEL            | セレクト信号 |

| Q0, Q1, Q2, Q3 | 出力信号   |

| input |    | output |    |    |    |

|-------|----|--------|----|----|----|

| A0    | A1 | Q0     | Q1 | Q2 | Q3 |

| 0     | 0  | 1      | 0  | 0  | 0  |

| 0     | 1  | 0      | 0  | 1  | 0  |

| 1     | 0  | 0      | 1  | 0  | 0  |

| 1     | 1  | 0      | 0  | 0  | 1  |

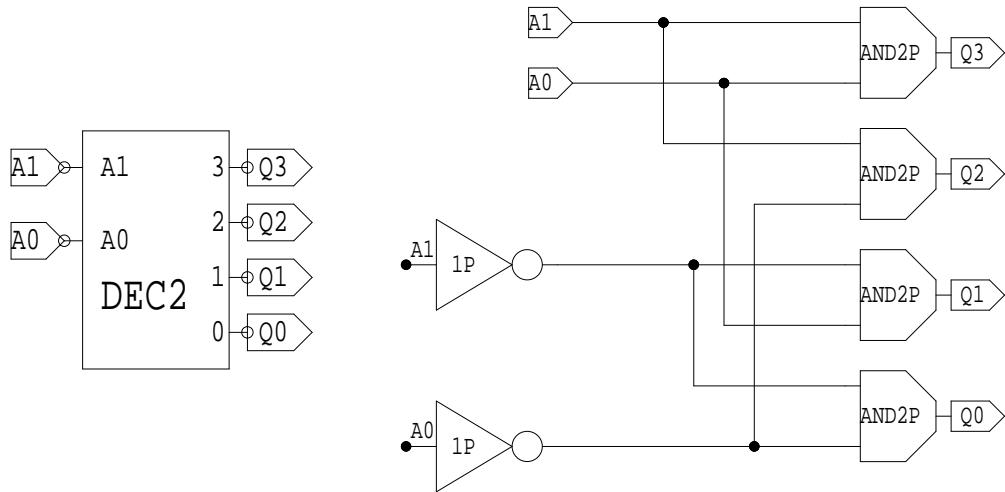

図 3.30 は DEC2B 回路の構成を示しており, NAND 回路, AND 回路, インバータとから構成される. COUNT8 からの入力信号を書き込む REGBNK4 回路を選択するためのデコーダである. SEL がハイレベルの状態で動作し, A0, A1 の入力信号の値に依って Q0 ~ Q3 の出力信号のいずれか一つがハイレベルになり, どの REGBNK4 に書き込むかを選択する. A0, A1 と Q0, Q1, Q2, Q3 の真理値表を表 3.12 に示した. なお, REGBNK4 回路を構成している DEC2B も同じ回路である.

### 3.5.4 DEC2N 回路

図 3.31: DEC2N 回路のシンボル (左) とその内部構成 (右)

表 3.14: DEC2N の真理値表

表 3.13: DEC2N 回路の素子・端子の機能

| 素子・端子名         | 機能     |

|----------------|--------|

| A1, A2         | 入力信号   |

| SEL            | セレクト信号 |

| Q0, Q1, Q2, Q3 | 出力信号   |

| input |    | output |    |    |    |

|-------|----|--------|----|----|----|

| A0    | A1 | Q0     | Q1 | Q2 | Q3 |

| 0     | 0  | 0      | 1  | 1  | 1  |

| 0     | 1  | 1      | 1  | 0  | 1  |

| 1     | 0  | 1      | 0  | 1  | 1  |

| 1     | 1  | 1      | 1  | 1  | 0  |

図 3.31 は DEC2N 回路の構成を示しており, NAND 回路, インバータとから構成される. COUNT8 からの入力信号を読み込む REGBNK4 回路を選択するためのデコーダである. SEL がハイレベルの状態で動作し, A0, A1 の入力信号の値に依って Q0 ~ Q3 の出力信号のいずれか一つがハイレベルになり, どの REGBNK4 から読み込むかを選択する. A0, A1 と Q0, Q1, Q2, Q3 の真理値表を表 3.14 に示した.

なお, REGBNK4 回路を構成している DEC2N も同じ回路である.

### 3.6 Glue 回路の構成

図 3.32: Glue 回路の構成

図 3.32 に Glue 回路の構成を示した . Glue 回路とは , ピクセルを結合して集積回路としてまとめた動作をするために必要な周辺回路をいう . 本回路における Glue 回路は CAPO , CAPXY 回路がそれぞれ一つずつあり , CAPB , CAPT が横方向に 6 個ずつ並び CAPL 回路が縦方向に 6 個ずつ並ぶ .

以下では Glue 回路を構成するそれぞれの回路について詳述する .

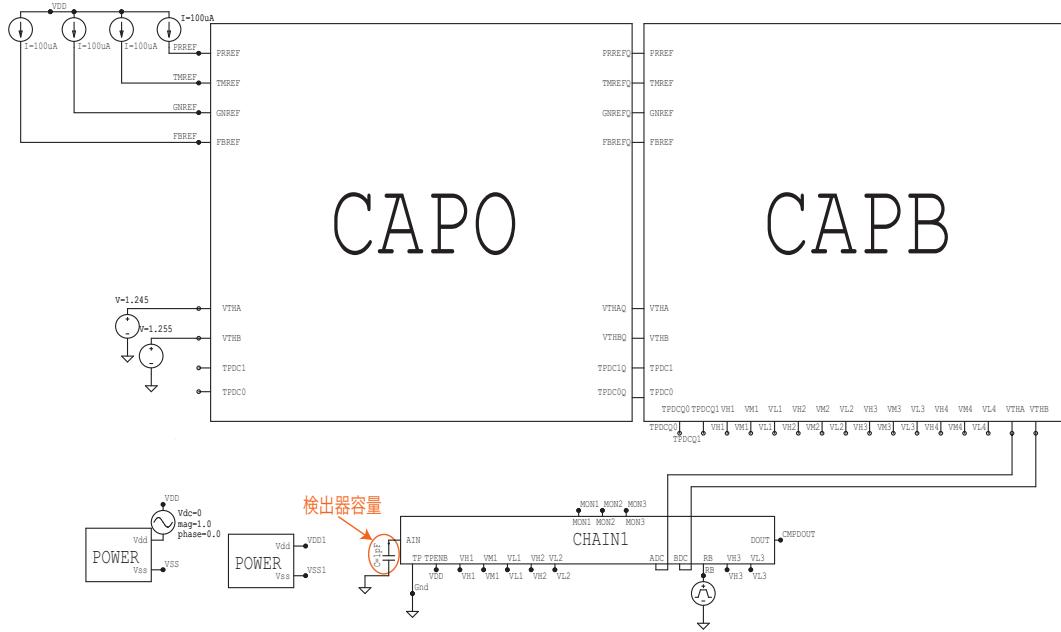

### 3.6.1 CAPO 回路

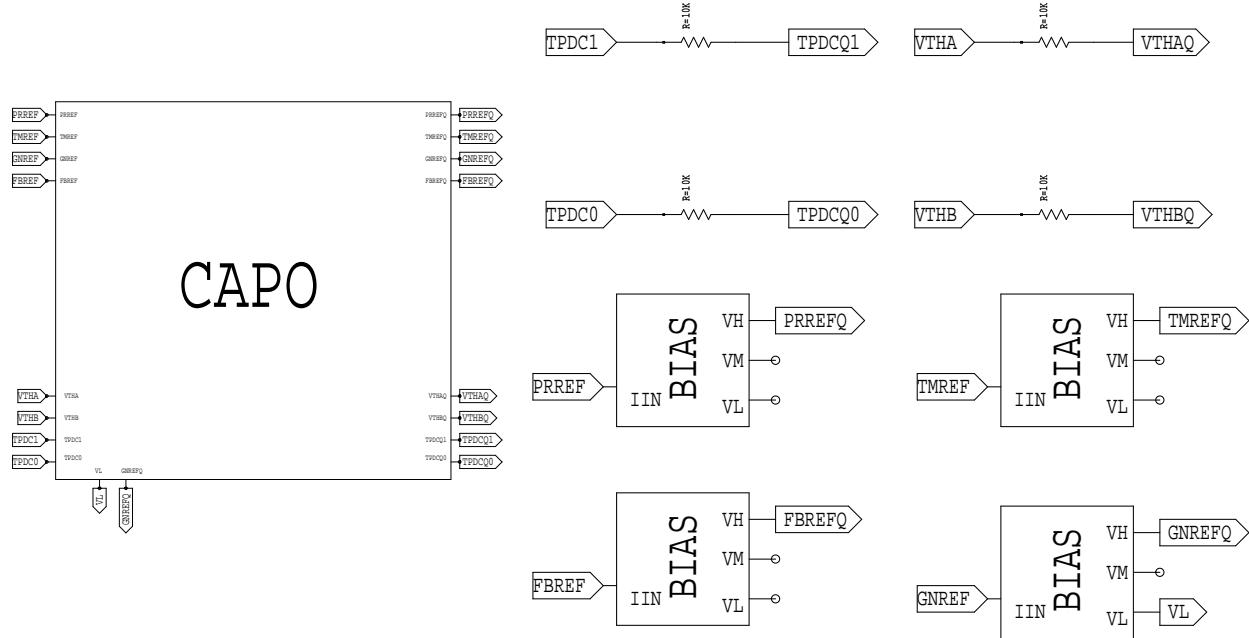

図 3.33: CAPO 回路のシンボル(左)とその内部構成(右)

表 3.15: CAPO 回路の素子・端子の機能

| 素子・端子名                         | 機能                       |

|--------------------------------|--------------------------|

| BIAS                           | バイアス回路                   |

| PRREF, TMREF, GNREF, FBREF     | バイアス電流                   |

| VTHA, VTHB                     | スレッショールド用入力信号            |

| TPDC1, TPDC0                   | テストパルス用入力信号              |

| VL                             | BIAS 回路出力の VL(0V) 基準電圧   |

| PRREFQ, TMREFQ, GNREFQ, FBREFQ | BIAS 回路出力の VH(2.5V) 基準電圧 |

| VTHAQ, VTHBQ                   | スレッショールド用出力信号            |

| TPDCQ1, TPDCQ0                 | テストパルス用出力信号              |

図 3.33 は CAPO 回路の構成を示している。CAPO 回路はアナログ信号の入出力を統括している。VTHA, VTHB, VTHAQ, VTHBQ は CHAIN1 回路における差動スレッショールドを与えるための入出力信号である。TPDC1, TPDC0, TPDCQ1, TPDCQ0 は CHAIN1 回路に入力するテストパルス用の入出力信号であり、CAPXY 回路の TPEXEC 信号がローレベルからハイレベルになるときに、テストパルスが TPDC0 の電圧から TPDC1 の電圧に変化することにより、パルスを発生させる。PRREF, FBREF, TMREF, GNREF はバイアス電流であり、BIAS 回路を通して VH(2.5V), VM(1.25V), VL(0V) の基準電圧に振り分けられる。PRREFQ, FBREFQ, TMREFQ, GNREFQ はそれぞれ PRREF, FBREF, TMREF, GNREF バイアス電流を BIAS

回路で  $VH$ (2.5V) の基準電圧にしたものである .  $VL$  は  $GNREF$  バイアス電流を  $BIAS$  回路で  $VL$ (0V) の基準電圧にしたものである .

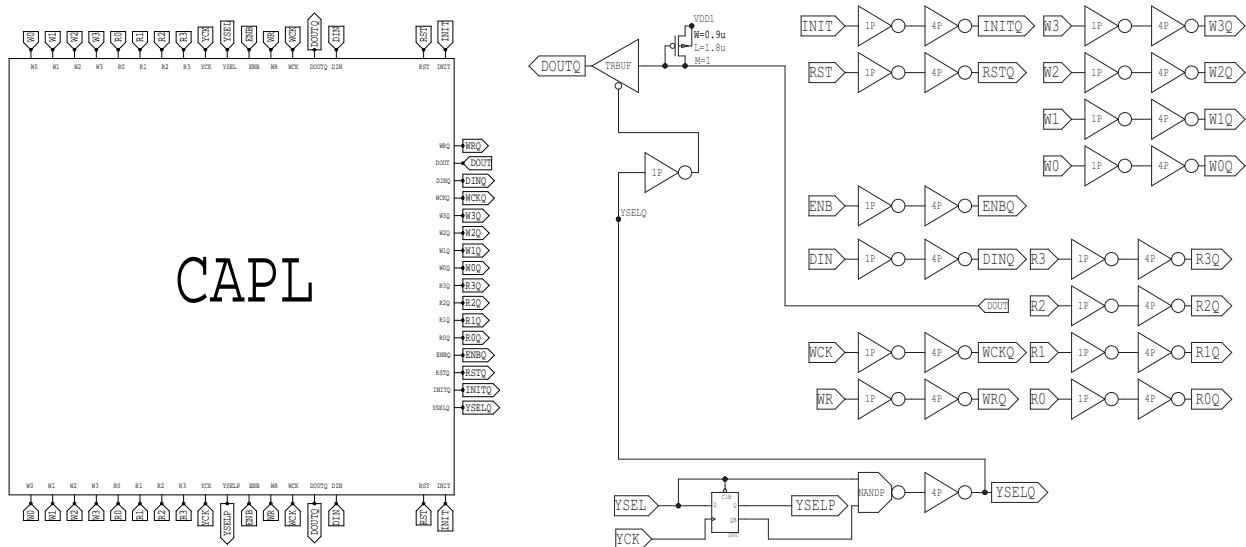

### 3.6.2 CAPB 回路

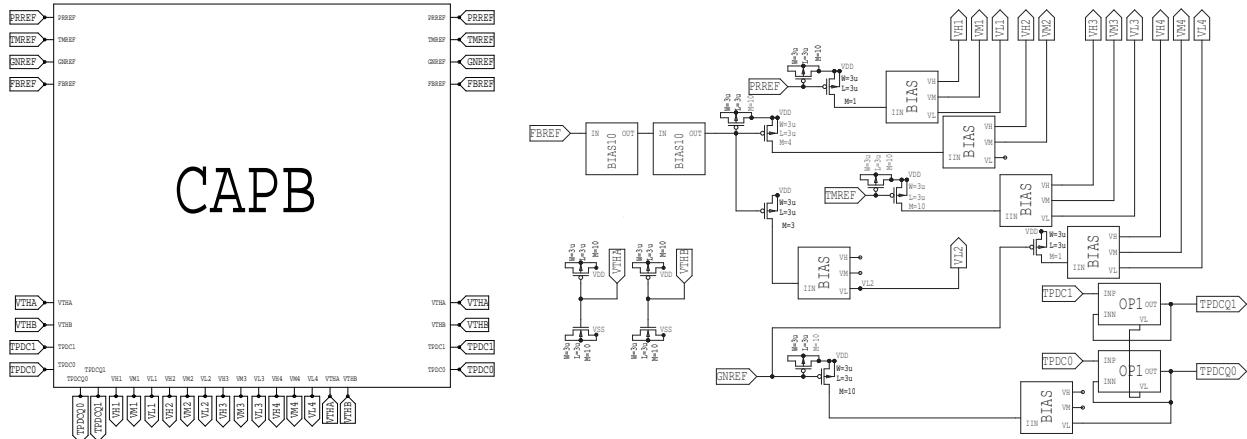

図 3.34: CAPB 回路のシンボル(左)とその内部構成(右)

表 3.16: CAPB 回路の素子・端子の機能

| 素子・端子名                     | 機能            |

|----------------------------|---------------|

| BIAS, BIAS10               | バイアス回路        |

| OP1                        | 増幅要素          |

| PRREF, TMREF, GNREF, FBREF | バイアス電圧        |

| VTHA, VTHB                 | スレッショールド用入力電圧 |

| TPDC0, TPDC1               | テストパルス用入力電圧   |

| VH1, VH2, VH3, VH4         | 2.5V 基準電圧     |

| VM1, VM2, VM3, VM4         | 1.25V 基準電圧    |

| VL1, VL2, VL3, VL4         | 0V 基準電圧       |

| TPDCQ0, TPDCQ1             | テストパルス用出力電圧   |

図 3.34 に CAPB 回路の構成を示している . CAPB 回路では CAPO 回路の出力信号を , さらにアナログ回路部において用いる基準電圧 , テストパルス用信号 , テストパルス用信号に振り分ける .  $VTHA$  ,  $VTHB$  は CHAIN1 回路における差動スレッショールドを与えるための入出力信号である .  $TPDC1$  ,  $TPDC0$  ,  $TPDCQ1$  ,  $TPDCQ0$  は CHAIN1 回路に入力するテストパルス用の入出力信号であり ,  $TPDC1$  ,  $TPDC0$  の入力信号を  $OP1$  を用いたユニティ・ゲイン・バッファ回路を通して出力した信号が  $TPDCQ1$  ,  $TPDCQ0$  の出力信号である .  $PRREF$  ,  $FBREF$  ,  $TMREF$  ,  $GNREF$  は バイアス電圧であり ,  $BIAS$  回路を通し , トランジスタで電流を変え , さらに  $BIAS$  回路で  $VL1$  ,  $VL2$  ,  $VL3$  ,  $VL4$  ,  $VM1$  ,  $VM2$  ,  $VM3$  ,  $VM4$  ,  $VH1$  ,  $VH2$  ,  $VH3$  ,  $VH4$  の基準電圧に変える .

### 3.6.3 CAPXY 回路

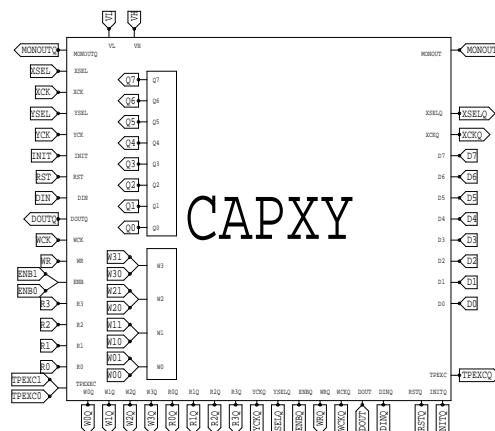

図 3.35: CAPXY 回路のシンボル

図 3.36: CAPXY 回路のシンボル (左) とその内部構成 (右)

表 3.17: CAPXY

| 素子・端子名                  | 機能                           |

|-------------------------|------------------------------|

| LVR                     | レシーバ回路                       |

| DFFC                    | フリップ・フロップ                    |

| BIASP                   | バイアス回路                       |

| OP1B                    | 増幅要素                         |

| VL                      | 0V 基準電圧                      |

| VH                      | 2.5V 基準電圧                    |

| MONOUT                  | CHAIN1 回路出力のモニタ波形入力信号        |

| D0,D1,D2,D3,D4,D5,D6,D7 | REGBNK4 回路出力信号の入力信号          |

| DOUT                    | CHAIN3 回路出力信号の入力信号           |

| XSEL                    | XSEL 信号                      |

| XCK                     | XCK 信号                       |

| YSEL                    | YSEL 信号                      |

| YCK                     | YCK 信号                       |

| INIT                    | CHAIN3 回路のフリップ・フロップリセット用入力信号 |

| RST                     | リセット入力信号                     |

| DIN                     | CHAIN3 回路のフリップ・フロップデータ用入力信号  |

| 素子・端子名                  | 機能                            |

|-------------------------|-------------------------------|

| WCK                     | CHAIN3 回路のフリップ・フロップ同期信号用入力信号  |

| WR                      | CHAIN3 回路のフリップ・フロップイネーブル用入力信号 |

| ENB1,ENB0               | イネーブル入力信号                     |

| R0,R1,R2,R3             | REGBNK4 の読み込み選択入力信号           |

| TPEXC1,TPEXC0           | テストパルス切り替え用入力信号               |

| W00,W01,W10,W11         | REGBNK4 の書き込み選択入力信号           |

| W20,W21,W30,W31         | REGBNK4 の書き込み選択入力信号           |

| MONOUTQ                 | CHAIN1 回路出力のモニタ波形出力信号         |

| DOUTQ                   | CHAIN3 回路出力信号の入力信号            |

| Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7 | REGBNK4 回路出力信号の出力信号           |

| W0Q,W1Q,W2Q,W3Q         | REGBNK4 の書き込み選択出力信号           |

| R0Q,R1Q,R2Q,R3Q         | REGBNK4 の読み込み選択出信号            |

| YCKQ                    | YCKQ 信号                       |

| YSELQ                   | YSELQ 信号                      |

| ENBQ                    | イネーブル出力信号                     |

| WRQ                     | CHAIN3 回路のフリップ・フロップイネーブル用出力信号 |

| WCKQ                    | CHAIN3 回路のフリップ・フロップ同期信号用出力信号  |

| DINQ                    | CHAIN3 回路のフリップ・フロップデータ用出力信号   |

| RSTQ                    | リセット出力信号                      |

| INITQ                   | CHAIN3 回路のフリップ・フロップリセット用入力信号  |

| XSELQ                   | XSELQ 信号                      |

| XCKQ                    | XCKQ 信号                       |

| TPEXCQ                  | テストパルス切り替え用出力信号               |

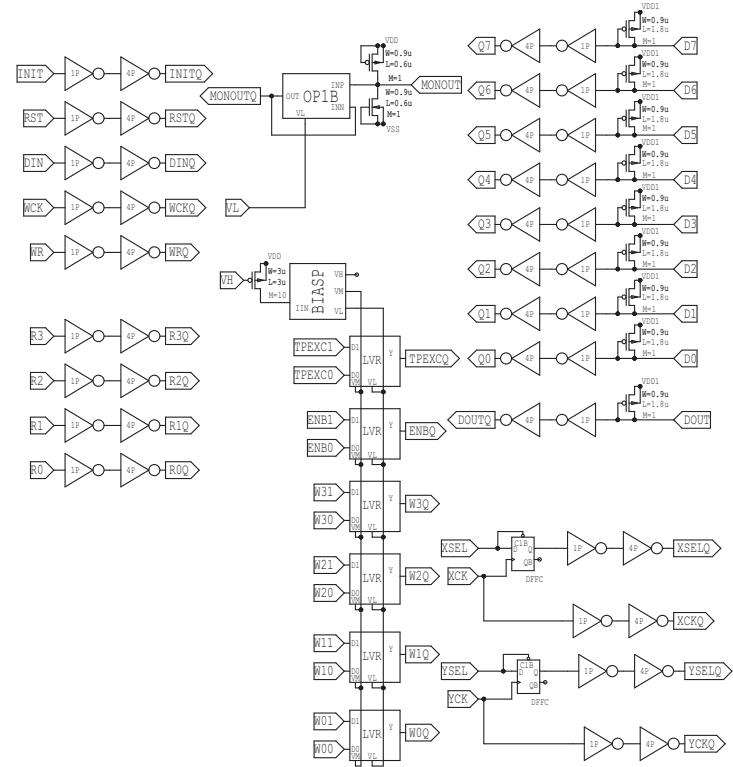

図 3.36 は CAPXY 回路の構成を示しており、増幅要素 OP1B、バイアス回路 BI-ASP、フリップ・フロップ DFFC CAPXY 回路はデジタル回路の全ての信号が通る。DFFC の一つは読み書きする CELLA の列を指定するシフトレジスタ回路の一部であり、XCK、XSEL の値に依って、XSELQ の値が変化する。もう一つの DFF は読み書きする CELLA の行を指定するシフトレジスタ回路の一部であり、YCK、YSEL の値に依って、YSELQ の値が変化する。

D0～D7、Q0～Q7 は CELLA のデジタル回路部における REGBNK4 回路からの出力信号が CAPT を通ってきた入出力信号である。MONOUT は CELLA のアナログ回路部における CHAIN1 回路のモニタ波形が CAPT を通ってきた入力信号であり、OP1B を用いたユニティ・ゲイン・バッファー回路を通って MONOUTQ が出力される。このとき、0V 基準電圧 VL がかかっているときに OP1B は動作する。WR、WRQ は CELLA のアナログ回路部における CHAIN3 回路のフリップ・フロップのイネーブル用入出力信号 WCK、WCKQ は CHAIN3 回路のフリップ・フロップの同期信号用入出力信号である。DIN、DINQ は CHAIN3 回路のフリップ・フロップのデータ用入出力信号である。INIT、INITQ は CHAIN3 回路のフリップ・フロップをリセットするための入出力信号である。RST、RSTQ は CHAIN3 回路のフリップ・フロップリセット用入力信号である。ENB0、ENB1、ENBQ は CELLA のデジタル回路

部における COUNT8 回路のイネーブル信号, 及び DEC2B 回路のセレクト信号用入出力信号である. W00 ~ W31, W0Q ~ W3Q は CELLA のディジタル回路部において COUNT8 の計数値を書き込む REGBNK4 回路を選択するための入出力信号である. R0 ~ R3, R0Q ~ R3Q は CELLA のディジタル回路部において COUNT8 の計数値を読み込む REGBNK4 回路を選択するための入出力信号である. TPEXEC1, 0 はテストパルスを発生させるための信号であり, TPEXEC1 がローレベルからハイレベルに変化するときに, パルスが発生する. VH(2.5V) はトランジスタを通して電流になり, BIASP 回路によって 1.25V 基準電圧 VM と 0V 基準電圧 VL とに振り分けられ, LVR 回路の電源となっている. LVR 回路は検出器からの微弱な信号に干渉して, アナログ信号の品質を劣化させるのを防ぐ役割を担っています.

### 3.6.4 CAPT 回路

図 3.37: CAPT 回路のシンボル (左) とその内部構成 (右)

表 3.18: CAPT 回路の素子・端子の機能

| 素子・端子名          | 機能             |

|-----------------|----------------|

| DFFC            | フリップ・フロップ      |

| SW0             | スイッチ回路         |

| TRBUF           | トライステート・バッファー  |

| XSEL            | XSEL 信号        |

| XCK             | XCK 信号         |

| TPEXEC          | テストパルス切り替え信号   |

| TPDC0,TPDC1     | テストパルス用入力信号    |

| VH1,VH2,VH3,VH4 | 2.5V 基準電圧      |

| VM1,VM2,VM3,VM4 | 1.25V 基準電圧     |

| VL1,VL2,VL3,VL4 | 0V 基準電圧        |

| VTHA,VTHB       | スレッシュホールド用入力信号 |

| 素子・端子名                  | 機能                   |

|-------------------------|----------------------|

| D0,D1,D2,D3,D4,D5,D6,D7 | REGBNK4 からの入力信号      |

| MONOUT                  | CHAIN1 回路のモニタ波形入力信号  |

| Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7 | トライステート・バッファーからの出力信号 |

| MONOUTQ                 | CHAIN1 回路のモニタ波形出力信号  |

| TPQ                     | テストパルス出力信号           |

| XSELQ                   | XSELQ 信号             |

| XSELP                   | XSELP 信号             |

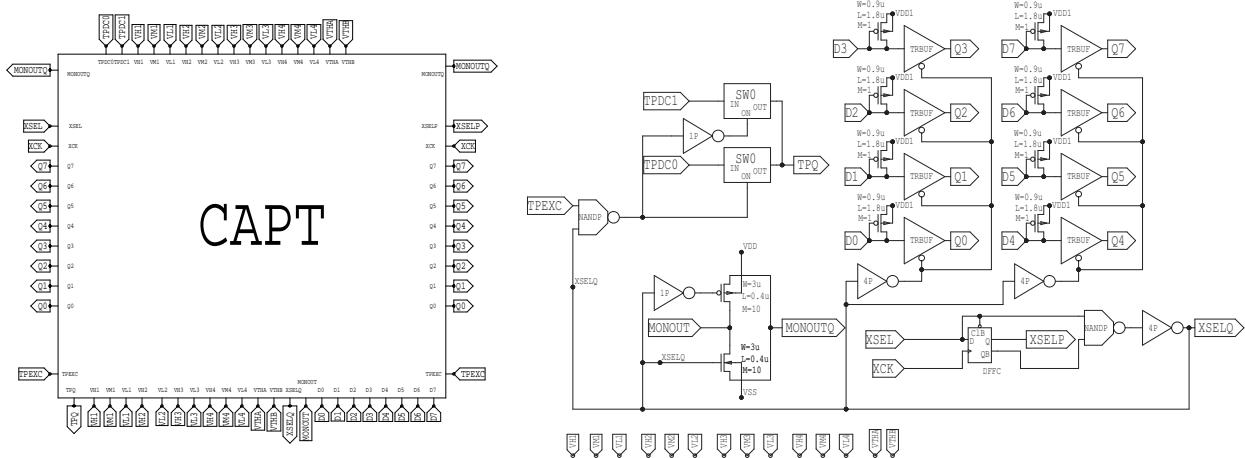

図 3.37 は CAPT 回路の構成を示しており、フリップ・フロップ DFFC、トライステート・バッファー TRBUF、スイッチ SW0、インバータとから構成される。DFFC は読み書きする CELLA の列を指定するシフトレジスタ回路の一部であり、XCK、XSEL の値に依って、XSELQ、XSELP の値が変化する。XSELQ がハイレベルの状態である CAPT の列の CELLA が選択され、トライステート・バッファー TRBUF が動作し、同時に TPEXEC がハイレベルのときにテストパルス出力 TPQ のスイッチ SW0 が動作する。D0～D7 は CELLA の REGBNK4 回路からの入力信号であり、トライステート・バッファーが動作しているとき、すなわち XSELQ がハイレベルのときには、それぞれ Q0～Q7 として出力する。TPEXEC は TPQ に影響を与え、XSELQ がハイレベルのもとで、TPEXEC がハイレベルであれば TPQ は TPDC0 と同電位になり、TPEXEC がローレベルであれば TPQ は TPDC1 と同電位になる。つまり、TPEXEC がローレベルからハイレベルに変化するところで、TPQ は TPDC0 の電位から TPDC1 の電位に変化し、その電位差のパルスを出力することになる。CELLA の CHAIN1 回路におけるスレッショールド電圧を与える VTHA、VTHB、0V 基準電圧 VL0～VL3、1.25V 基準電圧 VM0～VM3、2.5V 基準電圧 VH0～VH3 はそのまま CELLA に伝わる。

### 3.6.5 CAPL 回路

図 3.38: CAPL 回路のシンボル（左）とその内部構成（右）

表 3.19: CAPL 回路の素子・端子の機能

| 素子・端子名          | 機能                            |

|-----------------|-------------------------------|

| DFFC            | フリップ・フロップ                     |

| TRBUF           | トライステート・バッファー                 |

| W0,W1,W2,W3     | REGBNK4 の書き込み選択入力信号           |

| R0,R1,R2,R3     | REGBNK4 の読み込み選択入力信号           |

| YCK             | YCK 信号                        |

| YSEL            | YSEL 信号                       |

| ENB             | イネーブル信号                       |

| WR              | CHAIN3 回路のフリップ・フロップイネーブル用入力信号 |

| WCK             | CHAIN3 回路のフリップ・フロップ同期信号用入力信号  |

| DIN             | CHAIN3 回路のフリップ・フロップデータ用入力信号   |

| RST             | リセット信号                        |

| INIT            | CHAIN3 回路のフリップ・フロップリセット用入力信号  |

| DOUT            | CHAIN3 回路出力の DOUT 入力信号        |

| DOUTQ           | CHAIN3 回路出力の DOUT 出力信号        |

| YSELP           | YSELP 信号                      |

| WRQ             | CHAIN3 回路のフリップ・フロップイネーブル用出力信号 |

| DINQ            | CHAIN3 回路のフリップ・フロップデータ用出力信号   |

| WCKQ            | CHAIN3 回路のフリップ・フロップ同期信号用出力信号  |

| W3Q,W2Q,W1Q,W0Q | REGBNK4 の書き込み選択出力信号           |

| R3Q,R2Q,R1Q,R0Q | REGBNK4 の読み込み選択出力信号           |

| ENBQ            | イネーブル出力信号                     |

| 素子・端子名 | 機能                           |

|--------|------------------------------|

| RSTQ   | リセット出力信号                     |

| INITQ  | CHAIN3 回路のフリップ・フロップリセット用出力信号 |

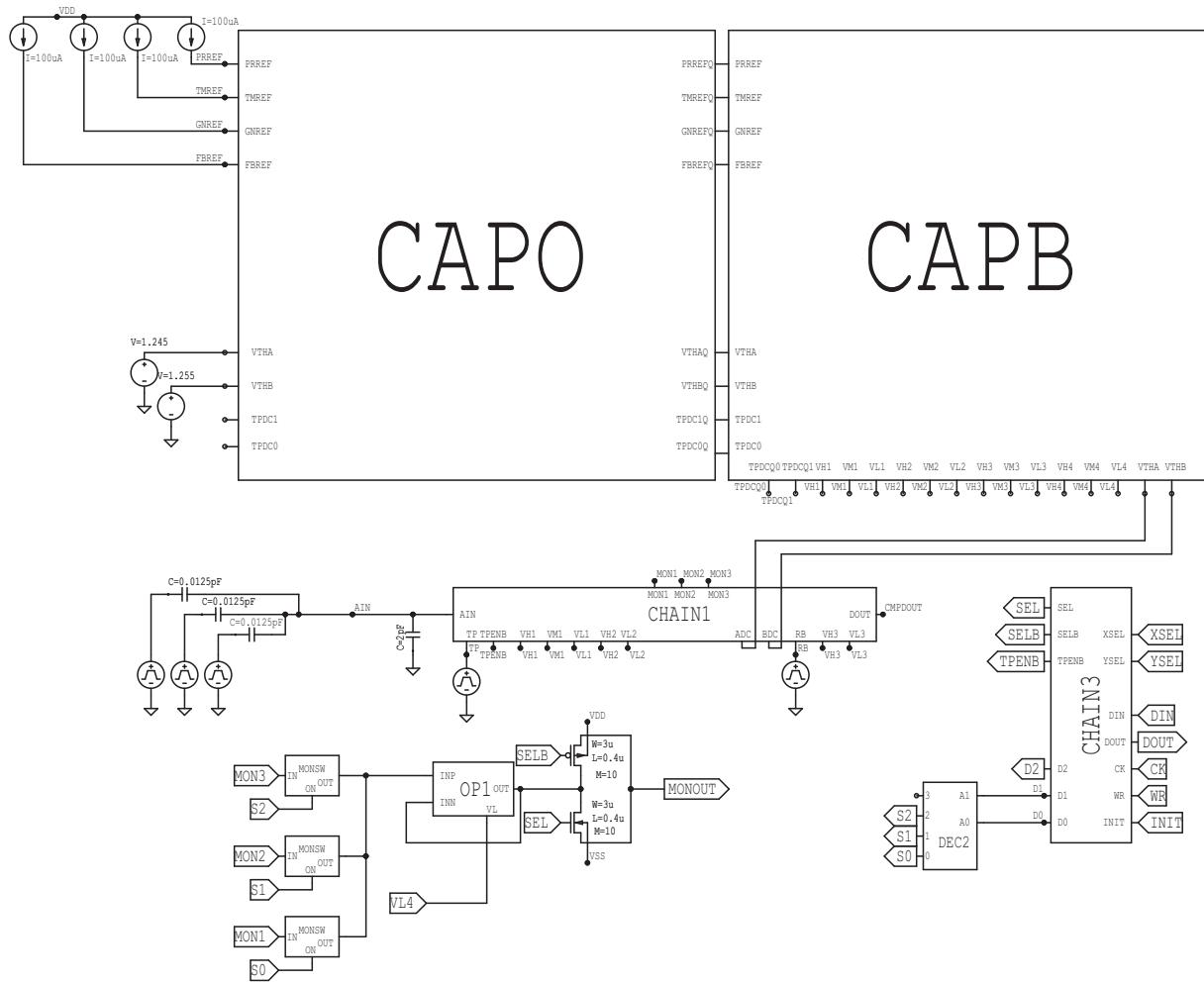

| YSELQ  | YSELQ 信号                     |

図 3.38 は CAPL 回路の構成を示しており、フリップ・フロップ DFFC、トライステート・バッファー TRBUF、NAND 回路、インバータとから構成される。DFFC は読み書きする CELLA の行を指定するシフトレジスタ回路の一部であり、YCK、YSEL の値に依って、YSELQ、YSELP の値が変化する。YSELQ がハイレベルの状態である CAPL の行の CELLA が選択され、トライステート・バッファー TRBUF が動作し、CELLA におけるアナログ回路部の CHAIN3 回路の出力である DOUTQ が出力される。W0～W3、W0Q～W3Q は CELLA のデジタル回路部において COUNT8 の計数値を書き込む REGBNK4 回路を選択するための入出力信号である。R0～R3、R0Q～R3Q は CELLA のデジタル回路部において COUNT8 の計数値を読み込む REGBNK4 回路を選択するための入出力信号である。WR、WRQ は CHAIN3 回路のフリップ・フロップのイネーブル用入出力信号 WCK、WCKQ は CHAIN3 回路のフリップ・フロップの同期信号用入出力信号である。DIN、DINQ は CHAIN3 回路のフリップ・フロップのデータ用入出力信号である。INIT、INITQ は CHAIN3 回路のフリップ・フロップをリセットするための入出力信号である。RST、RSTQ は CHAIN3 回路のフリップ・フロップリセット用入力信号である。ENB、ENBQ は CELLA のデジタル回路部における COUNT8 回路のイネーブル信号、及び DEC2B 回路のセレクト信号用入出力信号である。

# 第4章 回路シミュレーションを用いた評価試験

本章では前章までにおいて設計した回路に対してシミュレーションを用いた評価試験を行う。アナログ部においては SPICE シミュレーションを、デジタル部においては verilog シミュレーションを用いて評価試験を行う。

## 4.1 シミュレーションの手法

本研究回路はアナログ-デジタル混載型の回路であり、アナログ回路部とデジタル回路部の、それぞれについて別々にシミュレーションを行う。アナログ回路部においては、Tanner 社の S-Edit を用いて回路設計を行い、その S-Edit によってネットリストを作成し、同じく Tanner 社の T-Spice を用いて回路シミュレーションを行う。ここで、ネットリストとは回路の接続状態をテキストで示した情報である。SPICE とは Simulation Program with Integrated Circuit Emphasis の略であり、電子回路シミュレータである。本研究回路は 36 ピクセルから構成される回路であるが、シミュレーションに要する時間やパソコンのスペックの制限より SPICE シミュレーションは一つのピクセル回路について行う。アナログ回路シミュレーションでは、先ず検出器からの信号が 2 段の増幅器で増幅され、コンパレータでデジタル化される様子を観測する。次に、同様のシミュレーションを skew 条件、温度条件を変えて行う。続いて、電子雑音の影響、電源電圧のゆれに対する感度を調べる。最後に、ILC における実際の測定環境で 2 次光子等のバックグラウンドを除去するために設定されるスレッシュホールド電圧のもとでシミュレーションを行う。以上の回路シミュレーションによりアナログ回路部の評価を行う。

デジタル回路部においては verilog を用いた回路シミュレーションを行う。アナログ回路部から入力される信号を仮定し、その信号がカウント回路で計数される様子を観測する。また、カウント回路の計数値を全てのラッチ回路に読み書きし、漏れの無いシミュレーションを行う。ここで、verilog とはデジタル回路設計用の論理シミュレータである。

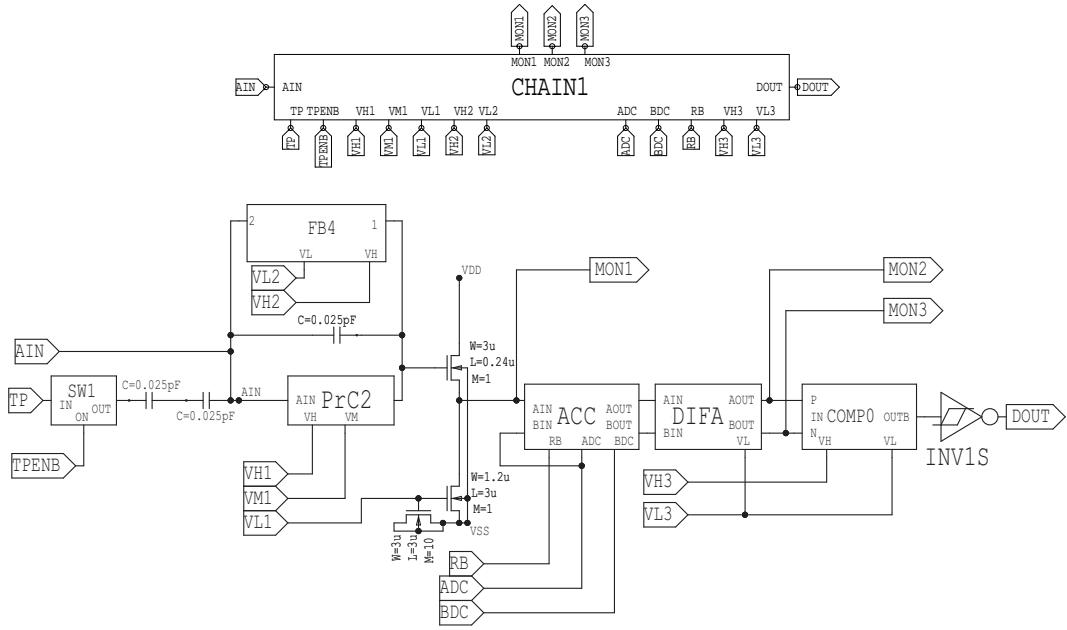

## 4.2 アナログ部

図 4.1: アナログ部の評価用回路図

図 4.2 はアナログ回路部の評価用の回路図である。アナログ回路の CHAIN1, モニタ回路, アナログ制御回路, 及びゲルーレ回路の CAPO, CAPB 回路からなる。CAPO 回路にはバイアス電流 PRREF, TMREF, GIREF, FBREF, 及びスレッショールド用電圧 VTHA, VTHB を入力している。ここで, テストパルス用電圧 TPDC0, TPDC1 は用いておらず, CHAIN1 回路に直接テストパルスを入力している。CHAIN1 回路には 1500ns に-400mV, 1800ns に-300mV, 2100ns に-200mV, 2400ns に-100mV の電圧を与えており, これらは 0.0125pF のコンデンサによりそれぞれ 31250, 23438, 15625, 7813 電子相当の負電荷インパルスに変えられて CHAIN1 回路に入力される。300ns には ACC 回路のスイッチ信号 (RB) を入力している。アナログ制御回路に入力する信号 DIN, CK, WR, INIT, XSEL, YSEL を調整して, CHAIN1 回路の MON1, MON2, MON3 の波形をそれぞれモニタできるようにしている。表 4.1 \* に上記セッ

\* アナログ制御回路の CHAIN3 に入力する信号である XSEL, YSEL, DIN, CK, WR, INIT については MON1, MON2, MON3 のいずれをモニタするかによって入力のタイミングなどが変わってくるため表には記載していない。詳細は 3.4.2 節のアナログ制御回路を参照。実際に入力している信号については図 3.21, 図 3.23, 図 3.25 を参照。

トアップにおける入力信号を整理した .

表 4.1: アナログ部の評価用回路図の入力信号

| 名称             | 値                | タイミング  |

|----------------|------------------|--------|

| VTHA           | 1.245V           | -      |

| VTHB           | 1.255V           | -      |

| PRREF          | $100\mu\text{A}$ | -      |

| TMREF          | $100\mu\text{A}$ | -      |

| GIREF          | $100\mu\text{A}$ | -      |

| FBREF          | $100\mu\text{A}$ | -      |

| 入力パルス 1 ( TP ) | -400mV           | 1500ns |

| 入力パルス 2        | -300mV           | 1800ns |

| 入力パルス 3        | -200mV           | 2100ns |

| 入力パルス 4        | -100mV           | 2400ns |

| RB             | 2.5V             | 300ns  |

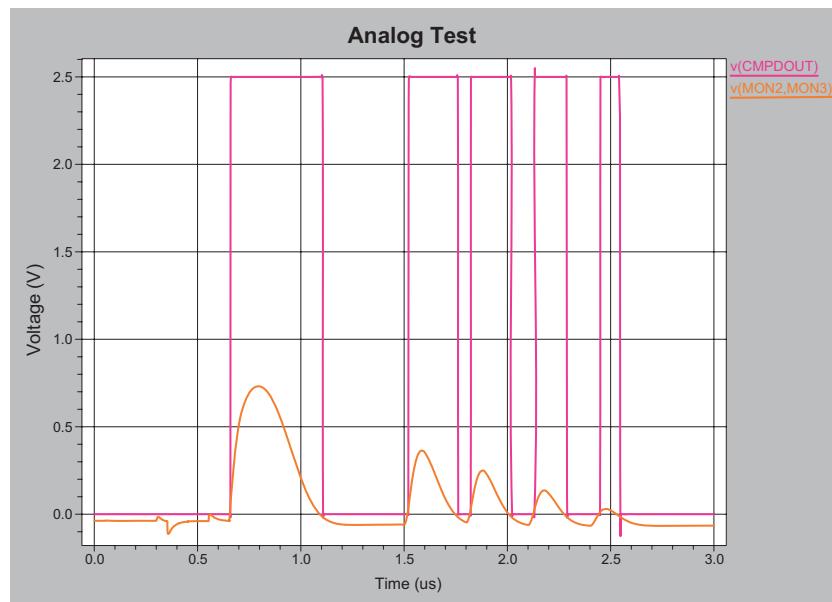

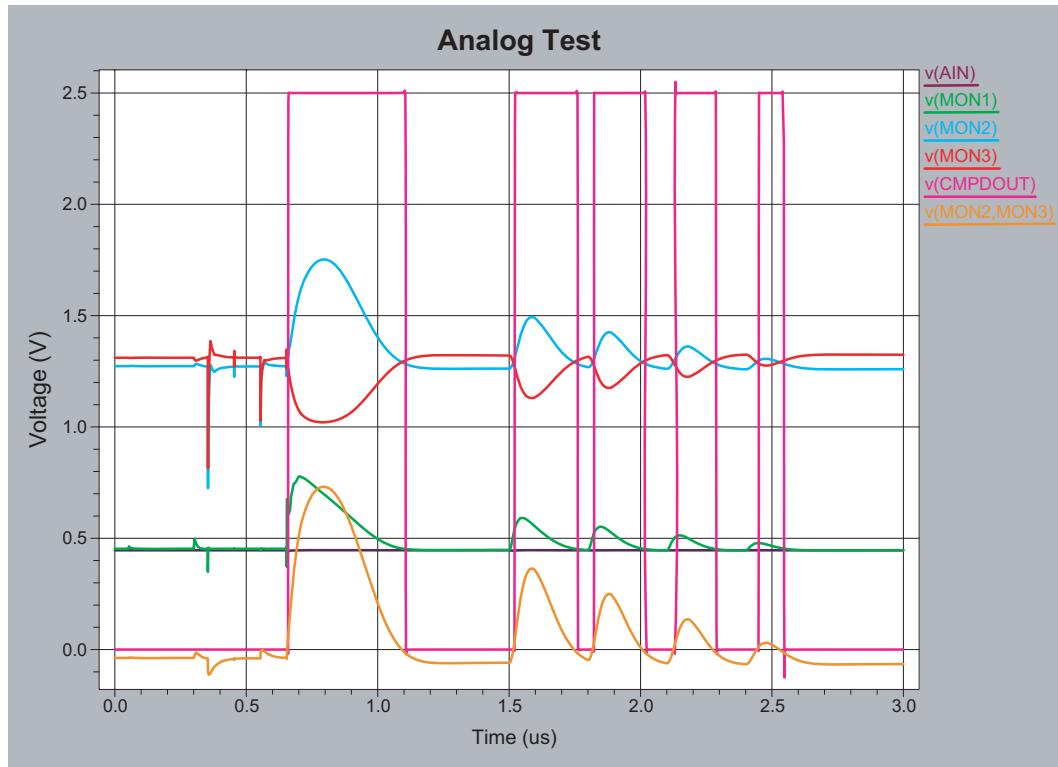

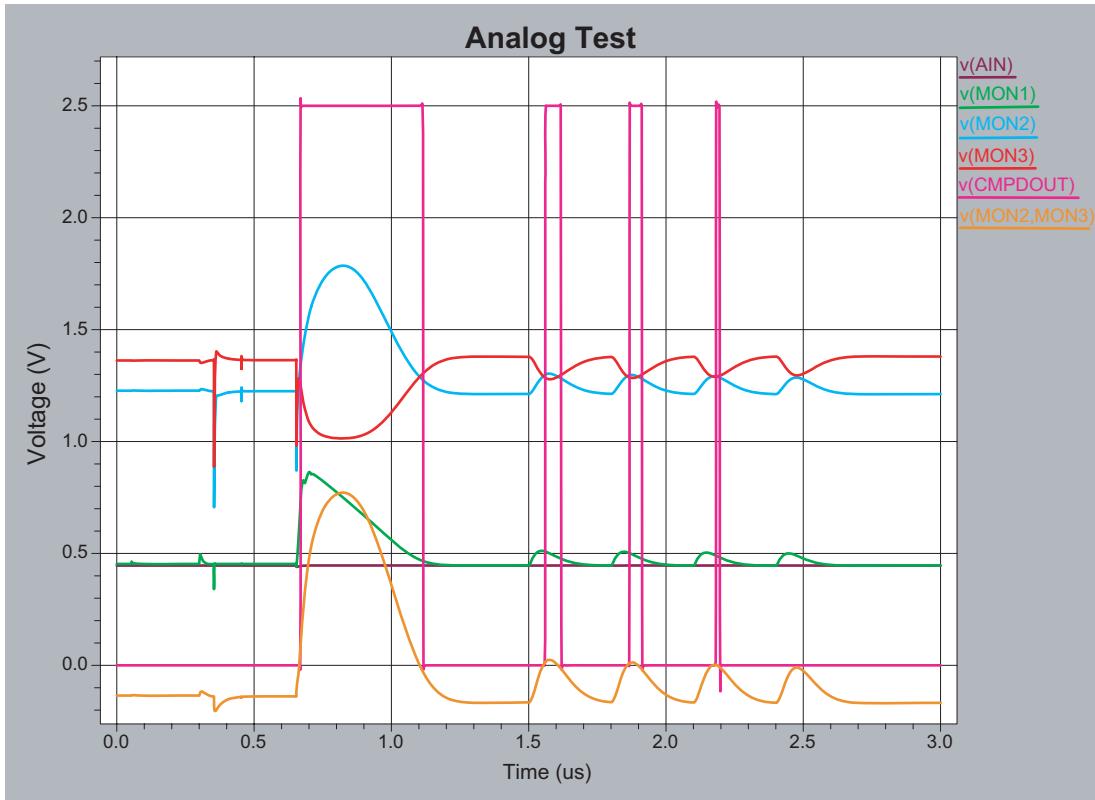

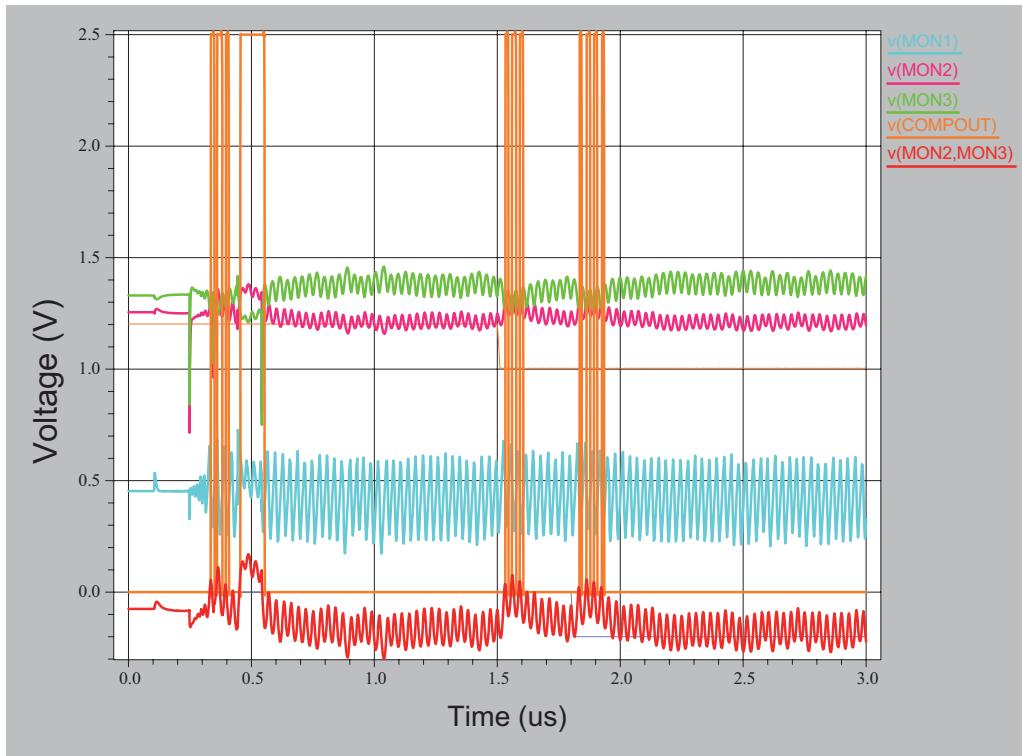

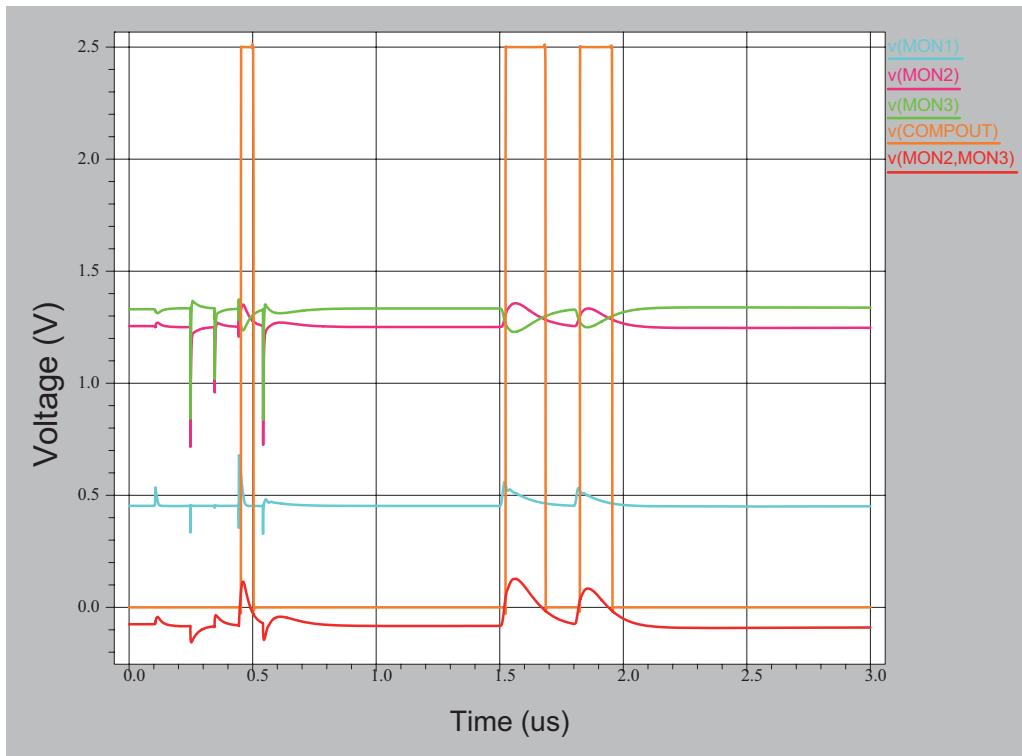

図 4.2 にテストパルス ( $v(TP)$ ), テストパルスも含めたすべての入力信号 ( $v(AIN)$ ), ソースフォロア回路からの出力信号 ( $v(MON1)$ ), 差動増幅回路サブブロックからの出力信号 ( $v(MON2)$  と  $v(MON3)$  及びそれらの差分をとった  $v(MON2,MON3)$ ), コンパレータ - の出力信号 ( $v(CMPDOUT)$ ) の信号波形を示した . ここで ,  $1.2\mu\text{s}$  より前の信号が乱れているのは , 700ns の TPENB 信号の影響である .

図より信号が大きい程ベースラインに戻るまでの時間が長くなり , コンパレータからの出力がハイレベルになっている時間が長くなっていることが判る . このことは非常に大きい信号が入力された場合には 300ns での信号の分離ができなくなることを意味している . ただし , 図では最大で 31250 の電子が入力した場合でも連続する信号が完全に分離されており , 3D シリコンピクセルセンサーからの典型的な信号スケールが 15000 電子程度であることを考えるとこれ以上の信号が入力されることはほとんどない . さらに , Pair Monitor は 35000 のピクセルからなり , 約 300ns 間隔のビームバンチにより対生成された電子 ( 陽電子 ) 群が同じピクセルに飛び込む可能性も小さい . 以上のことより , 本研究回路が機能しない場合というの非常に稀であり , 本研究回路は ILC のビーム構造を調べるのに十分な時間分解能を持った回路であると結論できる .

図 4.3 , 図 4.4 , 図 4.5 は図 4.2 の波形をモニタ回路で観測したときの波形である . MON1 , MON2 , MON3 の信号それがモニタできていることが分かる . ここで , モニタ波形が  $1.2\mu\text{s}$  より前で乱れているのは , モニタ回路において観測する信号を選択する信号が , まだ決定されていないためである .

図 4.2: アナログ部の評価テスト

図 4.3: モニタ回路で MON1 の波形を観測

図 4.4: モニタ回路で MON2 の波形を観測

図 4.5: モニタ回路で MON3 の波形を観測

#### 4.2.1 skew テスト

図 4.6 は図 4.2 のセットアップにおいて FF, TT, SS, FS, SF の 5 通りについてシミュレーションを行ったものである。pMOS トランジスタや nMOS トランジスタを生成するときにはある程度、半導体プロセス毎にトランジスタの性能に差がでてしまうことは避けることができない。そこで、その性能に最大限に差がついてしまった状態でも、正常に回路が動作するか確認するのが skew テストである。ここで、T は Typical, F は Fast, S は Slow を表しており、それぞれ典型的なトランジスタ、速いトランジスタ、遅いトランジスタを表す。そして、例えば skew 条件が FS とは、nMOS トランジスタが Fast で pMOS トランジスタが Slow であることを表している。

図 4.6 より、前置増幅器からの出力波形のベースラインの電圧が、skew 条件に依存して変化しているのが分かる。また、次段の差動増幅回路ブロックからの出力波形も skew 条件に影響を受けてベースラインの電圧が変化しているのが分かる。ただし、差動増幅回路からの 2 つの出力電圧の両方が skew 条件に依って同じ方向に変化している。そのため、差動増幅回路ブロックからの出力の差を取った波形には、ベースライン電圧、立ち上がり時間、ピーク電圧の変化がほとんどなく、またベースライン電圧に戻るまでの時間に若干の変化は見られるが、その変化は小さいものであり、ほとんど skew 条件による影響を受けていない。以上のことより、skew 条件を変化させた状態でも、本研究回路は十分な時間分解能を保ってアナログ信号をデジタル信号に変換することができる。つまり、本研究回路は十分な skew 条件に対する耐性を持っていると結論できる。

#### 4.2.2 温度テスト

図 4.7 は図 4.2 のセットアップにおいて -50, -25, 0, 25, 50 の 5 通りの場合についてシミュレーションしたものである。この図より、前置増幅器からの出力波形のベースラインの電圧が、温度に依存して変化していることが分かるが、次段の差動増幅回路ブロックからの出力波形はほとんど温度による影響を受けていない。そのため、差動増幅回路ブロックからの出力の差を取った波形も、ベースライン電圧、立ち上がり時間、ピーク電圧の変化がほとんどなく、またベースライン電圧に戻るまでの時間に若干の変化は見られるが、その変化は小さいものであり、ほとんど温度による影響を受けていない。以上のことより、温度条件を変化させた状態でも、本研究回路は十分な時間分解能を保ってアナログ信号をデジタル信号に変換することができる。つまり、本研究回路は十分な温度条件に対する耐性を持っていると結論できる。

図 4.6: Skew テスト

図 4.7: 温度テスト

### 4.2.3 電子雑音テスト

図 4.8: 電子雑音評価用セットアップ

図 4.8 にアナログ回路部の電子雑音の評価用回路図を示した。アナログ回路の CHAIN1, 及びゲルーレ回路の CAPO, CAPB 回路からなる。CAPO 回路にはバイアス電流 PRREF, TMREF, GIREF, FBREF, 及びスレッショールド用電圧 VTHA, VTHB を入力している。電子雑音の評価においてはテストパルスを入力する必要がないので, テストパルス用電圧 TPDC0, TPDC1 には信号を印加していない。300ns に ACC 回路のスイッチ信号 (RB) を入力している。電子雑音源として電流源 (isrc) を用いており, その周波数を 1kHz から 1GHz まで変化させている。表に上記セットアップにおける入力信号を整理した。

表 4.2: 電子雑音評価用回路図の入力信号

| 名称    | 値                | タイミング | 周波数領域       |

|-------|------------------|-------|-------------|

| VTHA  | 1.245V           | -     | -           |

| VTHB  | 1.255V           | -     | -           |

| PRREF | $100\mu\text{A}$ | -     | -           |

| TMREF | $100\mu\text{A}$ | -     | -           |

| GIREF | $100\mu\text{A}$ | -     | -           |

| FBREF | $100\mu\text{A}$ | -     | -           |

| isrc  | 1A ( 単位信号 )      | -     | 1kHz ~ 1GHz |

| RB    | 2.5V             | 300ns | -           |

検出器容量が  $0, 1, 2, 5, 10\text{pF}$  の 5 通りの場合について、差動増幅回路サブブロックからの出力信号の差をとったものに対しての雑音電圧を評価する。ここで、雑音としてはショット雑音、熱雑音、フリッカ雑音を考慮しており、雑音源としては抵抗、トランジスタ、検出器漏れ電流を挙げることができる。詳細は付録 A を参照。図 4.9、図 4.10 にその結果を示した<sup>†</sup>。図 4.9 は雑音スペクトルの周波数特性を示したものであり、図 4.10 は図 4.9 の雑音スペクトルを周波数領域で積分したものである。したがって、図 4.10 の高周波端での値が出力における雑音値を示していることになる。表 4.3 にそれぞれの検出器容量に対する 1A の単位信号の下での高周波端での電圧値、つまり雑音値と、その値を実際の入力雑音に換算し電子数で示した。ここで、雑音値を電子数に換算する際には  $31250\text{e}$  の電荷に対して  $421.35\text{mV}$  のパルス波高が得られたことを用いている。表 4.3 より検出器容量が数  $\text{pF}$  のレンジにおいては、電子雑音は高々  $500\text{e}$  程度であり、スレッショールドレベルを  $2000\text{e}$  と考えるならば測定に与える電子雑音の影響は十分に小さいと言つうことができる。

表 4.3: 入力容量と電子雑音の関係

| 入力容量 ( pF ) | 出力雑音 ( mV ) | 電子雑音への換算 ( e's ) |

|-------------|-------------|------------------|

| 0           | 2.38        | 177              |

| 1           | 4.49        | 333              |

| 2           | 7.24        | 537              |

| 5           | 15.28       | 1133             |

| 10          | 26.54       | 1968             |

<sup>†</sup>回路に入力する信号は 1A の単位信号であり、図が示す雑音の出力電圧はその 1A の入力信号に対するものである。得られた出力電圧を 4.2 節の結果を用いて実際の入力雑音に換算する。

図 4.9: 雑音スペクトル (周波数特性)

図 4.10: 雑音スペクトル (周波数領域での積分値)

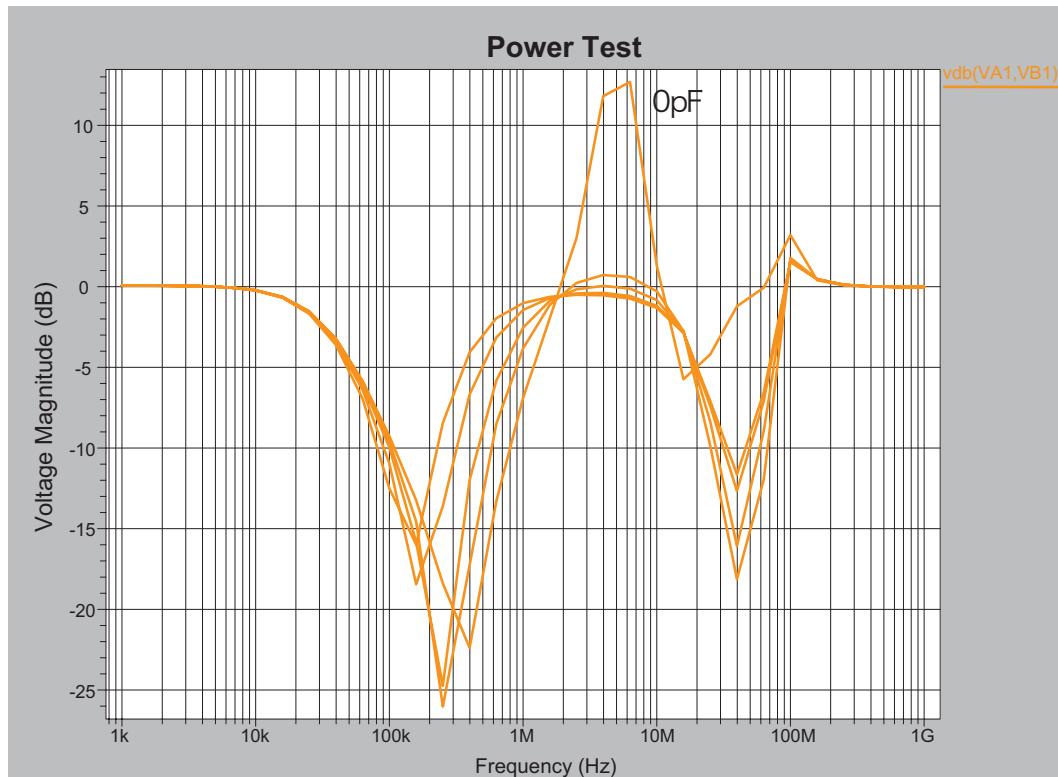

#### 4.2.4 電源電圧のゆれに対する感度

図 4.11: 電源電圧のゆれに対する感度の評価用セットアップ

図 4.11 に電源電圧のゆれに対する感度の評価用回路図を示した。アナログ回路の CHAIN1, 及びゲルーレ回路の CAPO, CAPB 回路からなる。CAPO 回路にはバイアス電流 PRREF, TMREF, GIREF, FBREF, 及びスレッショルド用電圧 VTHA, VTHB を入力している。電子雑音の評価においてはテストパルスを入力する必要がないので, テストパルス用電圧 TPDC0, TPDC1 は用いていない。300ns に ACC 回路のスイッチ信号 (RB) を入力している。2.5V のアナログ回路用電源 VDD に 1V の交流電源 (Vac) を接続し, その周波数を 1kHz から 1GHz で変化させている<sup>‡</sup>。表に上記セットアップにおける入力信号を整理した。

表 4.4: 電源電圧の揺れに対する感度評価用回路図の入力信号

| 名称    | 値                | タイミング | 周波数領域       |

|-------|------------------|-------|-------------|

| VTHA  | 1.245V           | -     | -           |

| VTHB  | 1.255V           | -     | -           |

| PRREF | $100\mu\text{A}$ | -     | -           |

| TMREF | $100\mu\text{A}$ | -     | -           |

| GIREF | $100\mu\text{A}$ | -     | -           |

| FBREF | $100\mu\text{A}$ | -     | -           |

| Vac   | 1V ( 単位信号 )      | -     | 1kHz ~ 1GHz |

| RB    | 2.5V ( ディジタル )   | 300ns | -           |

<sup>†</sup>1V の交流電源を用いているのは、1V を 0dB として出力の電圧振幅をデシベル表示するためであり、実際の電源電圧の揺れを 1V と評価しているわけではない。

検出器容量が 0,1,2,5,10 pF の 5 通りの場合について電源電圧を揺らし、差動増幅回路ブロックからの出力信号の差を取ったものに与える影響を 1kHz ~ 1GHz の周波数領域において周波数特性を調べることで評価する。図 4.12 にその結果を示した。ここで、振幅は 1V を 0dB としてデシベル表示で表している。検出器容量が 0 pF で周波数が 6 MHz 付近のときに最大 12.68 dB(4.3 倍) を示すが、電源電圧のゆれを  $100\mu\text{V}$  と考えても出力電圧のゆれは  $430\mu\text{V}$  程度であり、電子数に換算すると 32 電子程度と無視しても差し支えないレベルである。ここで、電圧値を電子数に換算する際には  $31250\text{e}$  の電荷に対して  $421.35\text{mV}$  のパルス波高が得られたことを用いている。

図 4.12: 電源電圧のゆれに対する感度テスト

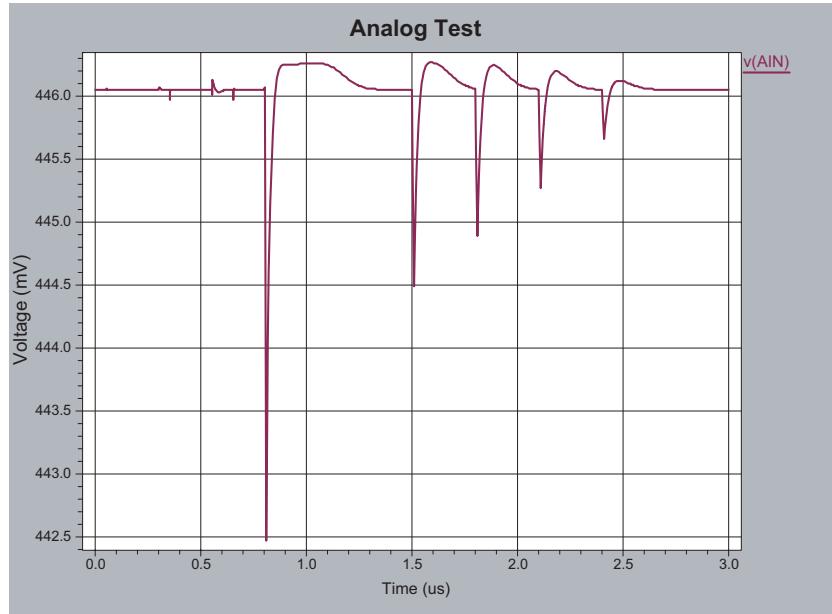

### 4.3 Pair Monitor のバックグラウンド処理のためのシミュレーション

図 4.13: Pair Monitor のバックグラウンド処理のためのシミュレーション結果

図 2.11において 70keV 以下の領域の分布は粒子のトラックが複数のピクセルにまたがって衝突したことによるバックグラウンドと、二次的な光子によるバックグラウンドの分布である。これらのバックグラウンドを取り除くために本研究回路では、外部から差動型のスレッショールド電圧を 70keV 相当の電圧に設定する。図 4.13 は図 4.2 のセットアップにおいて VTHA, VTHB, テストパルス, 検出器からの負電荷パルスの値を変えている。表 4.5 はそれらの値を記述したものである。

表 4.5: 本回路セットアップにおける入力信号

| 名称           | 値                                | タイミング                      |

|--------------|----------------------------------|----------------------------|

| VTHA         | 1.232V                           | -                          |

| VTHB         | 1.268V                           | -                          |

| テストパルス       | 14844e's                         | 1500ns                     |

| 検出器からの負電荷パルス | 13281e's<br>12969e's<br>12500e's | 1800ns<br>2100ns<br>2400ns |

図4.13より  $12969\text{e's}$  の電子の入力に対してはコンパレータが動作しているが、 $12500\text{e's}$  の電子の入力に対してはコンパレータが動作していない。 $12969\text{e's}$ 、 $12500\text{e's}$  をエネルギーに換算するとそれぞれ  $70\text{keV}$ 、 $68\text{keV}$  となる。つまり、上記のスレッショールドのセットアップにおいて、およそ  $70\text{keV}$  以下のバックグラウンドが除去できることが分かる。実際に本研究回路を使用する場合には、にはこれまでに見てきた skew 条件、温度条件、電子雑音、電源電圧のゆれなどを考慮し、差動スレッショールドの電位差を変化させる必要がある。多少バックグラウンドが含まれても、より多くの信号が必要なのであれば差動スレッショールドの電位差を小さくすればよいし、逆に信号を多少減らしても、バックグラウンドのないクリーンな環境で精密な測定を行いたいのであれば差動スレッショールドの電位差を大きくすればよい。

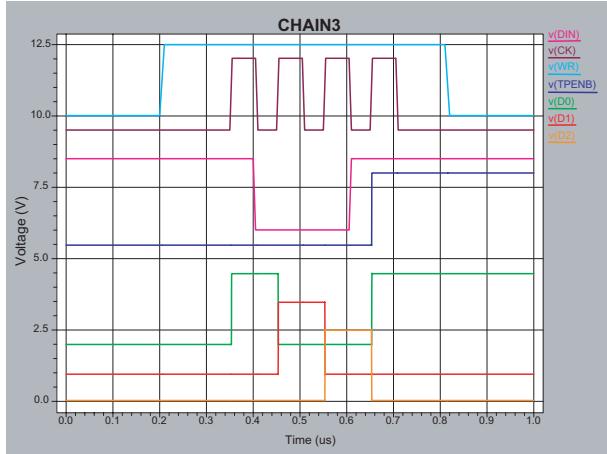

## 4.4 ディジタル部

### 4.4.1 verilog シミュレーション

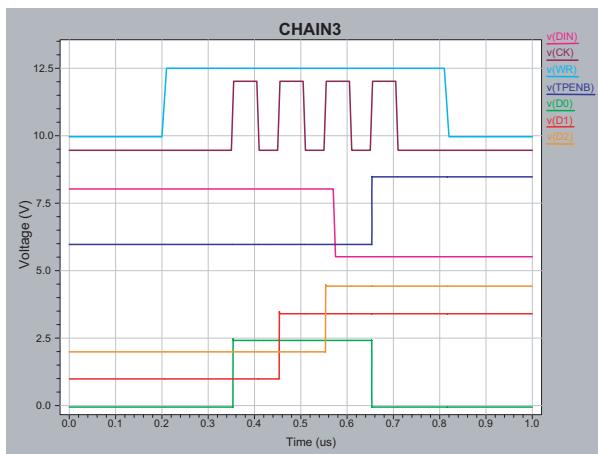

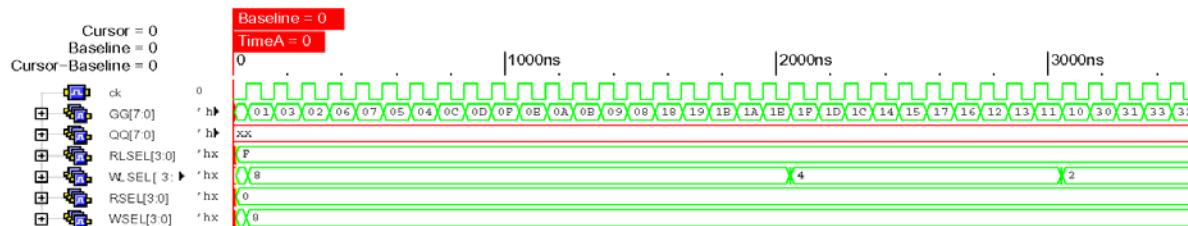

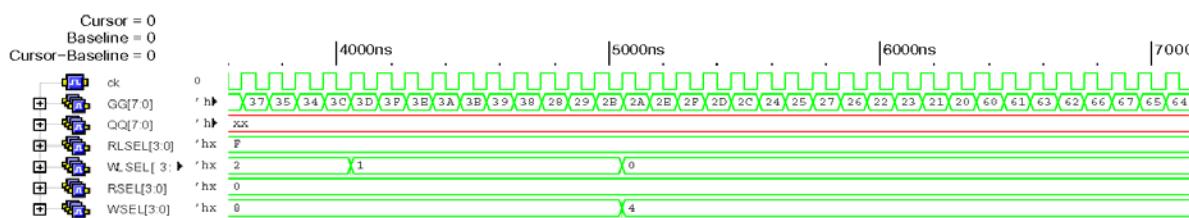

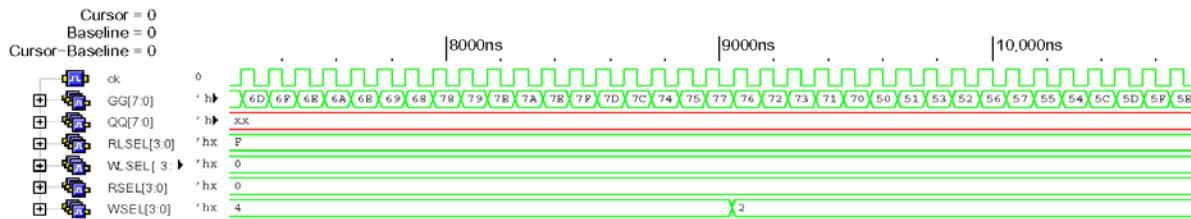

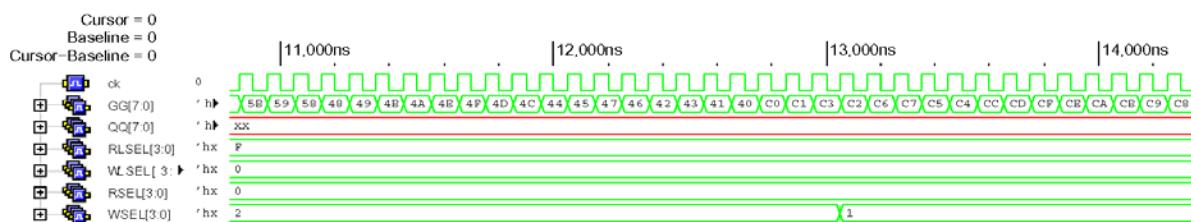

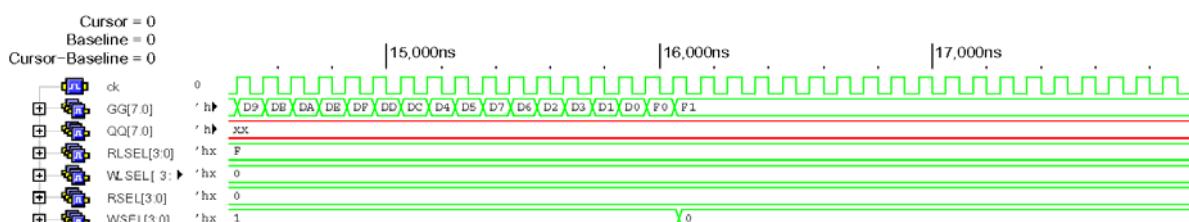

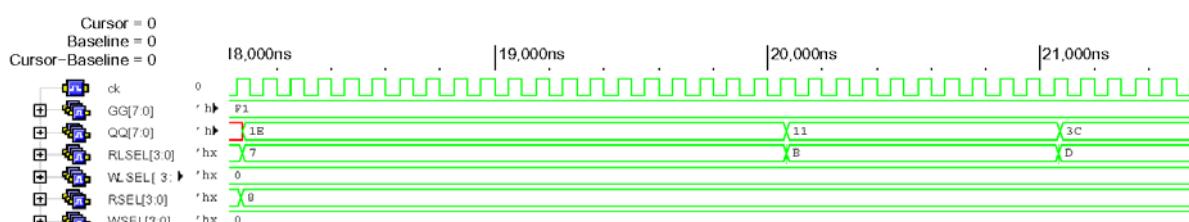

任意の LATCH8 を  $W0 \sim W3$ 、 $R0 \sim R3$  で選択した際に、呼び出し及び書き込みが期待されるように行われることを確認する。

図3.27のディジタル回路部には縦に4つのREGBNK4回路が並んでいて、それぞれのREGBNK4回路の中に4つのLATCH8回路が縦にならんでいる。つまり、全部で16のLATCH8回路が縦に並んでいることになる。それらのLATCH8回路の下から2番目から上に向かって順に書き込んでき、最後に一番下のLATCH8回路に書き込む。そして、全てのLATCH8回路に書き込みが終了したら、次に同じ順でLATCH8回路に保持してある値を読み出していく。モジュールには  $1\text{ns}$  の遅延を与えていて、それらのモジュールは実回路としては現れていない。

テストモジュールとしてシミュレーション時刻の基本単位である1ユニットを  $1\text{ns}$  に設定する。 $100\text{ns}$  周期のクロックをカウンターに入力し、そのクロックを計数する。計数は  $40\text{ns}$  から開始される。書き込みを行う間隔は計数開始からの経過時間で表すと、下から二番目のLATCH8回路は  $2000\text{ns}$ 、それよりも上の回路には書き込み時間を  $1000\text{ns}$  ずつ増やしていく。結局、一番上のLATCH8回路には計数開始から  $16000\text{ns}$  の間のクロックが書き込まれることになる。一番下のレジスタには計数開始から  $16020\text{ns}$  の間のクロックが書き込まれる。読み出しは  $20060\text{ns}$  から書き込みを行ったLATCH8回路の順に  $1000\text{ns}$  間隔で行われる。

$GG(b)$  は書き込まれるグレイコードの入力バイナリー表示であり、 $GG(h)$  は  $GG(b)$  の16進表示である。 $QQ(b)$  はテストモジュールから読み出される出力グレイコードのバイナリー表示であり、 $QQ(h)$  は  $QQ(b)$  の16進表示である。 $W$  は  $W0 \sim W3$  を並べた表示である。 $R$  は  $R0 \sim R3$  を並べた表示である。

図4.6にラッチを振る信号である  $W0, W1, R0, R1$  が変化したときを表示した。 $2040\text{ns} \sim 16040\text{ns}$  までは一番下以外のLATCH8回路については  $1000\text{ns}$  間隔で書き込むラッチが振られていることがわかる。 $20060\text{ns}$  から読み出しを行うが、 $16060\text{ns}$  までに書き込まれた数値が順番、値とも正しく読み出されていることがわかる。このストローブ条件では不定値がわからないが波形表示でみると数  $\text{ns}$  だが REGBNK4 が切り替わった直後に出力信号が乱れることがある。これは出力信号と切り替え信号のタイ

ミングにずれがあるためだと考えられる。しかし実際に出力信号を取り出す際には切り替わる直前に安定していれば良いので問題はない。

Verilogによるシミュレーションでは当該回路は期待通りに動いた。ゲートには1 nsの遅延時間と与えていたのでゲート遅延、配線で問題が生じることはないものと思われる。

表 4.6: ディジタル回路のシミュレーション結果

| 時間 (ns) | 信号レベル          |                |          |          |        |        |

|---------|----------------|----------------|----------|----------|--------|--------|

| 2040    | GG(b)=00011110 | QQ(b)=xxxxxxxx | GG(h)=1e | QQ(h)=xx | W=1000 | R=0000 |

| 3040    | GG(b)=00010001 | QQ(b)=xxxxxxxx | GG(h)=11 | QQ(h)=xx | W=0100 | R=0000 |

| 4040    | GG(b)=00111100 | QQ(b)=xxxxxxxx | GG(h)=3c | QQ(h)=xx | W=1100 | R=0000 |

| 5040    | GG(b)=00101011 | QQ(b)=xxxxxxxx | GG(h)=2b | QQ(h)=xx | W=0010 | R=0000 |

| 6040    | GG(b)=00100010 | QQ(b)=xxxxxxxx | GG(h)=22 | QQ(h)=xx | W=1010 | R=0000 |

| 7040    | GG(b)=01100101 | QQ(b)=xxxxxxxx | GG(h)=65 | QQ(h)=xx | W=0110 | R=0000 |

| 8040    | GG(b)=01111000 | QQ(b)=xxxxxxxx | GG(h)=78 | QQ(h)=xx | W=1110 | R=0000 |

| 9040    | GG(b)=01110111 | QQ(b)=xxxxxxxx | GG(h)=77 | QQ(h)=xx | W=0001 | R=0000 |

| 10040   | GG(b)=01010110 | QQ(b)=xxxxxxxx | GG(h)=56 | QQ(h)=xx | W=1001 | R=0000 |

| 11040   | GG(b)=01011001 | QQ(b)=xxxxxxxx | GG(h)=59 | QQ(h)=xx | W=0101 | R=0000 |

| 12040   | GG(b)=01000100 | QQ(b)=xxxxxxxx | GG(h)=44 | QQ(h)=xx | W=1101 | R=0000 |

| 13040   | GG(b)=11000011 | QQ(b)=xxxxxxxx | GG(h)=c3 | QQ(h)=xx | W=0011 | R=0000 |

| 14040   | GG(b)=11001010 | QQ(b)=xxxxxxxx | GG(h)=ca | QQ(h)=xx | W=1011 | R=0000 |

| 15040   | GG(b)=11011101 | QQ(b)=xxxxxxxx | GG(h)=dd | QQ(h)=xx | W=0111 | R=0000 |

| 16040   | GG(b)=11110000 | QQ(b)=xxxxxxxx | GG(h)=f0 | QQ(h)=xx | W=1111 | R=0000 |

| 16060   | GG(b)=11110001 | QQ(b)=xxxxxxxx | GG(h)=f1 | QQ(h)=xx | W=0000 | R=0000 |

| 20060   | GG(b)=11110001 | QQ(b)=00011110 | GG(h)=f1 | QQ(h)=1e | W=0000 | R=1000 |

| 21060   | GG(b)=11110001 | QQ(b)=00010001 | GG(h)=f1 | QQ(h)=11 | W=0000 | R=0100 |

| 22060   | GG(b)=11110001 | QQ(b)=00111100 | GG(h)=f1 | QQ(h)=3c | W=0000 | R=1100 |

| 23060   | GG(b)=11110001 | QQ(b)=00101011 | GG(h)=f1 | QQ(h)=2b | W=0000 | R=0010 |

| 24060   | GG(b)=11110001 | QQ(b)=00100010 | GG(h)=f1 | QQ(h)=22 | W=0000 | R=1010 |

| 25060   | GG(b)=11110001 | QQ(b)=01100101 | GG(h)=f1 | QQ(h)=65 | W=0000 | R=0110 |

| 26060   | GG(b)=11110001 | QQ(b)=01111000 | GG(h)=f1 | QQ(h)=78 | W=0000 | R=1110 |

| 27060   | GG(b)=11110001 | QQ(b)=01110111 | GG(h)=f1 | QQ(h)=77 | W=0000 | R=0001 |

| 28060   | GG(b)=11110001 | QQ(b)=01010110 | GG(h)=f1 | QQ(h)=56 | W=0000 | R=1001 |

| 29060   | GG(b)=11110001 | QQ(b)=01011001 | GG(h)=f1 | QQ(h)=59 | W=0000 | R=0101 |

| 30060   | GG(b)=11110001 | QQ(b)=01000100 | GG(h)=f1 | QQ(h)=44 | W=0000 | R=1101 |

| 31060   | GG(b)=11110001 | QQ(b)=11000011 | GG(h)=f1 | QQ(h)=c3 | W=0000 | R=0011 |

| 32060   | GG(b)=11110001 | QQ(b)=11001010 | GG(h)=f1 | QQ(h)=ca | W=0000 | R=1011 |

| 33060   | GG(b)=11110001 | QQ(b)=11011101 | GG(h)=f1 | QQ(h)=dd | W=0000 | R=0111 |

| 34060   | GG(b)=11110001 | QQ(b)=11110000 | GG(h)=f1 | QQ(h)=f0 | W=0000 | R=1111 |

| 35060   | GG(b)=11110001 | QQ(b)=11110001 | GG(h)=f1 | QQ(h)=f1 | W=0000 | R=0000 |

書き込み

読み出し

# 第5章 チップ製作

本章では以上のとおり設計された回路を集積化し，一つのチップとして製作するためのプロセスの流れ，及び個々のプロセスについて記述する．

## 5.1 チップ製作のプロセス

チップ製作のプロセスは以下のステップから成る．

- レイアウト設計・デバイス設計

- DRC，及びLVSによるレイアウト検証作業

- チップ製造

レイアウト設計は(株)デジアン・テクノロジー社の協力で行われた．また，本チップ試作は東京大学大規模集積システム設計教育研究センター(VDEC)を通し，MOSISの協力で行われたものである．MOSISではチップの試作製造サービスとしてマルチプロジェクト・ウェーハ(MPW)サービスを提供している．MPWサービスとは，複数の大学や企業から製造を依頼されたチップ・デザインを1枚のウェーハに載せて製造を行い、製造されたウェーハを切り分けて，チップ・デザインごとに以来元の大学や企業に提供するサービスのことである．そのため，少量のチップ製造でも安価に行うことができる．我々が試作依頼したチップの仕様は表5.1の通りである．

表 5.1: 試作チップの仕様

|        |                                    |

|--------|------------------------------------|

| チップサイズ | 4mm × 4mm                          |

| 製造プロセス | TSMC0.25 $\mu$ m CMOS プロセス         |

| オプション  | deep-nwell*，5層メタル，MIM <sup>†</sup> |

| ピン数    | 128 <sup>‡</sup>                   |

\*deep-n-wellでは通常のプロセスよりも深いn-well領域を作り，その領域内にp-well領域を作ることでp-well領域を他から孤立させることができる．そのため，p-well領域と他の領域との干渉を防ぐことができる．本研究回路はデジタル・アナログ混載回路であるが，アナログ回路ブロックをdeep-n-well領域内に作ることで，デジタル回路ブロックとアナログ回路ブロックとの間の干渉を防ぐことができる．

<sup>†</sup>MIM(Metal Insulator Metal)とは容量絶縁膜を金属ではさむ構造のことであり，高容量化，高密度化が可能である．本研究回路におけるキャパシターに利用されている構造である．

<sup>‡</sup>具体的なピン配置は付録Bを参照．

## 5.2 レイアウト , デバイス設計

レイアウト , デバイス設計に関しては , 作業を依頼した ( 株 ) デジアン・テクノロジー社に本回路の内容を十分理解していただいた上で , それに適した形で設計を進めていただいた . その上で , 本回路のレイアウトにあたって , 特別に要求のある点は事前に伝えておき , そのほかの点についても疑問が生じた場合はこちらに確認していただくという形で作業は進められた .